ДАННЫЕ И ПРОГРАММЫ

Содержание этой главы носит в основном справочный характер. В ней приведены лишь основные понятия и самые общие сведения о работе микро-ЭВМ, без которых неподготовленному читателю будет трудно проследить работу основных ее узлов, описанию которых посвящены последующие главы книги. Читатель, знакомый с основами построения ЭВМ и программирования, может сразу перейти к следующей главе.

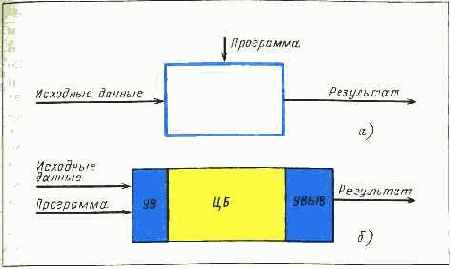

Как уже говорилось в предыдущей главе, чтобы решить задачу на машине, нужно ее запрограммировать; т. е. составить определенную последовательность команд (программу), которая, вместе с данными должна быть введена в память машины. В процессе решения задачи центральный процессор обращается к памяти машины, выполняет команды, извлеченные из памяти, обрабатывает в соответствии с этими командами данные, извлеченные из той же памяти и полученные от внешних устройств, и в зависимости от результатов обработки переходит к выполнению одной или нескольких других команд. Последовательность команд, приводящая к решению задачи, называется программой решения задачи. Каждая машина характеризуется определенным набором операций (системой команд), или машинным языком, которые должны быть известны пользователю, решающему свою задачу на данной машине.

Чтобы машина могла воспринимать передаваемые ей команды и данные, они должны быть представлены в двоичной форме. С этой целью каждой команде ставится в соответствие двоичный код, а все числовые значения выражаются в двоичной системе счисления.

Под двоичной системой счисления подразумевается позиционная весомозначная система с основанием 2 и с цифрами 0,1. Термин "позиционная весомозначная" означает, что в зависимости от положения цифры в числе ей приписываются разные значения, или вес. В наиболее распространенных системах счисления этот вес равен степени основания, показатель которой ра-вен n — 1, где п — номер разряда, отсчитываемый справа налево. Системы счисления получают наименование в зависимости от основания.

Так, в десятичной системе счисления основанием является 10, в двоичной — 2, в восьмеричной — 8, в шестнадца-теричной — 16 и т. п. При этом количество используемых цифр для представления чисел равно основанию системы счисления. В двоичной системе используются всего две цифры: 0 и 1. В десятичной системе используются 10 цифр от 0 до 9, в восьмеричной — восемь цифр, т. е. первые восемь цифр десятичной системы (от 0 до 7). В шестнадцатеричной системе счисления используются все цифры десятичной системы, а в качестве недостающих шести цифр используются первые шесть букв латинского алфавита: А, В, С, D, Е, F. Примеры записи десятичных чисел от 0 до 16 и от 248 до 255 в двоичной, восьмеричной и шестнадцатеричной системах счислений приведены в табл. 3.1. Десятичное число 255 является наибольшим представимым в двоичной системе счисления при условии использования всего восьми разрядов для записи чисел. Для представления чисел, больших 255, необходимо в двоичной системе счисления использовать большее число разрядов.

Чтобы отличить число, записанное в той или иной системе счисления, от числа, записанного в другой системе счисления, в конце записи обычно ставят соответствующие используемому основанию цифры или буквы (иногда в виде индексов, например 3810). Для десятичной системы счисления часто используется буква D, для двоичной — В, для восьмеричной — Q, для шестнадцатеричной — Н. Например:

216 D = 11011000 В = 330 Q = D8 Н.

Как следует из табл. 3.1, наиболее громоздким из рассмотренных представлений, в особенности для больших чисел, является двоичное представление, а наиболее компактным — шестнадца-теричное представление, не совсем удобное для восприятия. Чтобы воспользоваться числовыми результатами в шестнадцатеричной системе счисления, необходимо перевести их в более привычную десятичную форму. Способы перевода чисел из одной системы счисления в другую неоднократно описывались в литературе и здесь рассматриваться не будут.

Таблица 3.1

|

Представление чисел |

|||||

|

Десятичное |

Двоичное |

Восьмеричное |

Шестнадцате-ричное |

||

|

0 |

00000000 |

000 |

00 |

||

|

1 |

00000001 |

001 |

01 |

||

|

2 |

00000010 |

002 |

02 |

||

|

3 |

00000011 |

003 |

03 |

||

|

4 |

00000100 |

004 |

04 |

||

|

5 |

00000101 |

005 |

05 |

||

|

6 |

00000110 |

006 |

06 |

||

|

7 |

00000111 |

007 |

07 |

||

|

8 |

00001000 |

010 |

08 |

||

|

9 |

00001001 |

011 |

09 |

||

|

10 |

00001010 |

012 |

ОА |

||

|

11 |

00001011 |

013 |

0В |

||

|

12 |

00001100 |

014 |

ОС |

||

|

13 |

00001101 |

015 |

OD |

||

|

14 |

00001110 |

016 |

ОЕ |

||

|

15 |

00001111 |

017 |

OF |

||

|

16 |

00010000 |

020 |

10 |

||

|

248 |

11111000 |

370 |

F8 |

||

|

249 |

11111001 |

371 |

F9 |

||

|

250 |

11111010 |

372 |

FA |

||

|

251 |

11111101 |

373 |

FB |

||

|

252 |

11111100 |

374 |

FC |

||

|

253 |

11111101 |

375 |

FD |

||

|

254 |

11111110 |

376 |

FE |

||

|

255 |

11111111 |

377 |

FF |

||

не совсем удобно ввиду непривычности использования буквенных обозначений числовых величин.

Весьма распространенным способом представления данных и команд является их восьмеричное представление. Оно довольно компактно и легко переводимо в двоичную форму. Для этого достаточно запомнить двоичные коды трех первых двоичных разрядов (см. табл. 3.1). Перевод двоичного числа в восьмеричное производится следующим образом. Двоичный код разбивается справа налево на триады, каждая триада считается самостоятельным двоичным кодом трехразрядного числа и заменяется соответствующей цифрой от 0 до 7. Перевод восьмеричного кода в двоичный производится аналогичным образом: каждая цифра от 0 до 7 заменяется соответствующим двоичным кодом.

Пусть, например, требуется записать восьмеричный код восьмиразрядного двоичного числа 10110101 В. Разбитый на триады двоичный код будет 10 НО 101 В. После замены каждой триады двоичным кодом получим 265 Q. Двоичное представление восьмеричного числа 312Q получается также просто: 11 001 010 В или 11001010 В.

Представление двоичных чисел в табл. 3.1 в виде восьмиразрядных кодов приведено не случайно. Наименьшей единицей информации, которая может быть представлена в ЭВМ, является двоичный разряд или бит. Бит может иметь два значения: О или 1, а соответствующий ему электрический сигнал — два уровня напряжения. Группа из восьми двоичных разрядов называется байтом. Более крупными единицами информации являются килобит (1024 = 210 бит, или двоичных разрядов), килобайт (1024 = 210 байт) и мегабайт (1048576 =220 байт). Иногда выделяют группу из четырех двоичных разрядов, называемую ниблом. Этим понятием пользуются при рассмотрении процессов выполнения арифметических операций в двоично-десятичных кодах.

Остановимся теперь на определении понятия машинной команды как элемента записи машинной программы.

Под командой подразумевается указание, записанное на машинном языке микро-ЭВМ и определяющее ее действия при выполнении отдельной операции или части вычислительного процесса. Команда может быть представлена в символической форме или в форме кодов (шестнадцатеричных, восьмеричных, двоичных). Таким образом, под программой подразумевается фиксированная последовательность команд, воспринимаемых машиной как единая целая группа указаний, позволяющая решить поставленную пользователем задачу.

В качестве формального языка для описания данных и программ их обработки на микро-ЭВМ используются не только машинный язык, но и специальные языки программирования, такие как, например, БЕЙСИК. Программа на таком языке, называемом иногда языком высокого уровня, не может непосредственно восприниматься микропроцессором. В совершенных ЭВМ специальная программа, называемая интерпретатором или компилятором, преобразует программу на языке высокого уровня в эквивалентную ей программу на языке машины.

Программа, написанная на языке Ассемблер, переводится пользователем в машинные восьмеричные коды с помощью таблицы кодов (табл. 4.1 — 4,3) и вводится вместе с данными также в восьмеричных кодах в ПМ-ЭВМ с клавиатуры и размешается в оперативном запоминающем устройстве, в котором выделяется специальная область, где пользователь может разместить свою программу.

Процесс размещения программы в памяти может быть легко представлен с помощью простой модели запоминающего устройства, имеющей вид обычного книжного стеллажа или открытой полки, разделенной на отдельные ячейки. Каждой ячейке присвоен номер, называемый адресом. В ячейку можно поместить данные ограниченного объема: один байт или восьмиразрядный двоичный код. Команда, занимающая три машинных слова (три байта), может быть размещена лишь в трех ячейках памяти. При этом первый байт размещается в ячейке по указанному адресу, а остальные два — в последующих ячейках памяти. Важно при этом правильно поместить начальную команду программы, которая должна находиться в той ячейке, с которой микропроцессор начинает свою работу.

Программа для ПМ-ЭВМ представляет собой последовательность указанных кодов, из которых левый код — адрес ячейки памяти, а правый — команда или данные.

Предположим, что соответствующие программе и исходным данным найденные коды введены в ПМ-ЭВМ, На чем основаны процессы преобразования всей этой информации в машине?

ДРУГИЕ ВОЗМОЖНОСТИ ПМ-ЭВМ

В этой главе мы рассмотрели расширение возможностей ПМ-ЭВМ в части клавиатуры и индикации, памяти, внешнего накопителя и ТВ-дисплея. Обслуживание всех этих устройств осуществлялось программным путем, без значительного усложнения схемы самой ПМ-ЭВМ и ее устройств ввода/вывода. Программное обслуживание внешних устройств со стороны центрального процессора требует больших затрат машинного времени за счет исполнения основной программы и снижает производительность вычислительной системы. Использование прерываний, прямого доступа к памяти (ПДП) и программируемых периферийных микросхем позволяет повысить производительность и гибкость вычислительной системы. Периферийные программируемые микросхемы являются специализированными периферийными процессорами, берущими на себя часть задач центрального процессора. При этом техническая сложность системы зачастую не возрастает или даже уменьшается.

Отечественной промышленностью выпускается широкая номенклатура периферийных программируемых микросхем, со-гласуемых с МП типа КР580ВМ80А.

Использование программируемых микросхем в конкретной МП-системе связано: 1) с заданием режимов ее работы в системе, адресацией и определением электрических связей с внутренними шинами МП-системы и периферийными устройствами; 2) с вводом фрагмента программы, задающей режимы работы микросхемы (программа инициализации); 3) с обращением к микросхеме в процессе исполнения рабочей программы.

Количественный рост МП-системы ведет и к ее архитектурному усложнению. Возникает необходимость каким-либо образом стандартизовать связи микро-ЭВМ. Известно много стандартов внутрисистемных шин МП-систем. Для МП серии КР580ИК80А наиболее известны шины MULTIBUS и 8=100, позволяющие объединять в систему периферийные, процессорные блоки и блоки памяти различных изготовителей.

Большая МП-система требует специального математического обеспечения (МО). Если при написании и отладке программ емкостью до 1 Кбайт можно с успехом обойтись программированием в кодах, то программы большего размера пишутся обычно на языках различных уровней, в том числе и на специализированных языках высокого уровня.

Для перевода таких программ на машинный язык необходимы программы-интерпретаторы, а для отладки — программы редактирования и отладки. Чтобы весь комплекс программ мог успешно функционировать, необходимо использовать какую-либо операционную систему (ОС). Все это доводит общую емкость МО до нескольких сотен килобайт и требует для хранения специальных накопителей. Поэтому не имеет смысла, как говорят, "с нуля" проектировать большую МП-систему. Гораздо разумнее использовать уже имеющийся опыт, взяв в качестве образца готовую промышленную систему.

Для любой системы, состоящей из заданного набора элементов, есть предел сложности, определяемый надежностью входящих в нее элементов, надежностью связей между элементами, допусками при проектировании, программным обеспечением, архитектурой системы, внешними условиями и теми функциями, которые система должна выполнять. Не ставьте перед собой сверхзадач и не переусложняйте систему, иначе она будет неработоспособной. Имейте мужество отказаться от дальнейшего наращивания уже имеющейся системы, когда ее надежность падает до неприемлемого уровня, чтобы заново перепроектировать систему на современном идеологическом и техническом уровне.

Рассмотрим коротко характеристики некоторых программируемых микросхем, находящих широкое применение в МП-системах.

Микросхема программируемого последовательного интерфейса типа КР580ВВ51А является универсальным синхронно-асинхронным приемопередатчиком (УСАПП), предназначенным для осуществления связи в последовательном формате между МП-системой и внешним абонентом. Микросхема используется как периферийное устройство, программируемое центральным процессором МП-системы почти для любого стандартного протокола последовательной передачи данных. Микросхема принимает данные от МП-no шине данных в параллельном формате и преобразует их в непрерывный поток последовательных данных для передачи абоненту. Микросхема может одновременно с этим принимать последовательные данные, преобразовывать их в параллельный формат и передавать микропроцессору.

Она сигнализирует микропроцессору о готовности к приему нового слова, предназначенного для передачи абоненту в последовательном формате, а также о готовности передать МП-принятое от абонента слово. МП-может в любой момент времени считать из микросхемы слово состояния, указывающее на возможные ошибки при приеме информации и содержащее признаки наличия управляющих сигналов.

Микросхема типа КР580ВИ53 представляет программируемый таймер/счетчик, предназначенный для работы в качестве периферийного устройства МП-системы. Микросхема состоит из трех независимых 16-битовых счетчиков с максимальной частотой счета 2 МГц. Каждый счетчик микросхемы может работать в одном из шести запрограммированных режимов. С помощью микросхемы таймера/счетчика решается одна из наиболее часто встречающихся в МП-системах задач — генерирование точных программно задаваемых временных задержек взамен организации холостых программных циклов. Пользователь подключает соответствующим образом микросхему, загружает один из счетчиков нужным числом, после чего в результате подачи команды счетчик отсчитывает заданную задержку и вырабатывает сигнал прерывания для МП-системы. Микросхема может выполнять функции не только генератора задержки, но и программируемого генератора заданной частоты, счетчика событий, датчика реального времени и др.

Микросхема типа КР580ВВ55А представляет собой программируемый периферийный интерфейс, предназначенный для приема в МП-систему и выдачи из нее информации в параллельном коде, функции микросхемы в системе задаются программно, поэтому, как правило, не требуется подключать какие-либо дополнительные логические схемы. Предназначенные для ввода и вывода внешней информации 24 ножки микросхемы могут быть индивидуально запрограммированы группами по 12 и использованы в трех различных режимах работы. В первом из них (Режим 0) в каждой группе из 12 ножек часть может быть запрограммирована на ввод, а часть — на вывод.

Во втором режиме ( Режим 1) группа программируется так, что 8 ножек служат для ввода или вывода, а 3 ножки из оставшихся 4 предназначены для сигналов квитирования (запрос — подтверждение) и прерывания. В третьем режиме (Режим 2) из 8 ножек организуется 8-разрядная двунаправленная шина, а 5 ножек (с за-емом из другой группы) предназначены для сигналов квитирования и прерывания.

Микросхема типа КР580ВТ57 представляет собой четырех-канальный программируемый контроллер прямого доступа к памяти (ПДП), предназначенный для организации высокоскоростного обмена данными между периферийными устройствами и памятью МП-системы, построенной на базе микропроцессора КР580ВМ80А. Функция микросхемы заключена в основном в

мы имеют информационную емкость 2К х 8 и программируются побайтно импульсами на ТТЛ-уровне. Микросхема приводится в исходное состояние (когда во всех разрядах стоят единицы) путем облучения ультрафиолетовым источником света, в качестве которого можно использовать с соответствующими предосторожностями обычную бытовую кварцевую лампу, а в качестве программатора — саму ПМ-ЭВМ.

ПРИЛОЖЕНИЯ

Система команд микропроцессора КР580ИК80А

ПРИЛОЖЕНИЕ1

|

Мнемокод команды |

Описание команды |

Длина команды байт |

, Изменяемые флаги |

Число тактов |

|

INRr |

Увеличение содержимого регистра г на еди- |

1 |

Z,S,P,AC |

5 |

|

|

ницу |

|

|

|

|

INRM |

Увеличение на единицу содержимого ячейки |

1 |

Z,S,P,AC |

10 |

|

|

памяти по адресу, указанному в регистрах Н |

|

|

|

|

|

и L |

|

|

|

|

DCRr |

Уменьшение содержимого регистра г на еди- |

1 |

Z,S,P, AC2 |

5 |

|

|

ницу |

|

|

|

|

DCRM |

Уменьшение на единицу содержимого ячейки |

1 |

Z, S,P, AC2 |

10 |

|

|

памяти по адресу, указанному в регистрах Н |

|

|

|

|

|

иЬ |

|

|

|

|

MOVrl,r2 |

Пересылка данных из регистра г 2 в регистр rl |

1 |

- |

5 |

|

MOV M, г |

Пересылка данных из регистра г в ячейку па- |

1 |

- |

7 |

|

|

мяти по адресу, указанному в регистрах Н и L |

|

|

|

|

MOV г, М |

Пересылка данных в регистр г из ячейки памя- |

1 |

- |

7 |

|

|

ти по адресу, указанному в регистрах Н и L |

|

|

|

|

ADDr |

Суммирование содержимого регистра г и со- |

1 |

Z,S,P,C,AC |

4 |

|

|

держимого аккумулятора |

|

|

|

|

ADDM |

Суммирование содержимого ячейки памяти |

1 |

Z,S,P,C, AC |

7 |

|

|

по адресу, указанному в регистрах Н и L, |

|

|

|

|

|

с содержимым аккумулятора |

|

|

|

|

ADCr |

Сложение с учетом переноса содержимого ре- |

1 |

Z,S,P, C, AC |

4 |

|

|

гистра г и содержимого аккумулятора |

|

|

|

|

ADCM |

Сложение с учетом переноса содержимого |

1 |

Z,S,P,C,AC |

7 |

|

|

ячейки памяти по адресу, указанному в ре- |

|

|

|

Продолжение прилож. 1

|

Мнемокод команды |

Длина Описание команды команды, Изменяемые флаги байт |

Число тактов |

|

|

ги страх Н и L, с содержимым аккумулятора |

|

|

SUB r |

Вычитание содержимого регистра г из содер- 1 Z,S,P, С , АС |

4 |

|

|

жимого аккумулятора |

|

|

SUBM |

Вычитание из содержимого аккумулятора 1 Z, S, Р, С , АС |

7 |

|

|

содержимого ячейки памяти по адресу, ука- |

|

|

|

занному в регистрах Н и L |

|

|

SBBr |

Вычитание с заемом содержимого регистра г 1 Z, S, Р, С , АС |

4 |

|

|

из содержимого аккумулятора |

|

|

SBBM |

Вычитание с заемом из содержимого аккуму- 1 Z,S,P,C , AC |

7 |

|

|

лятора содержимого ячейки памяти по адресу, |

|

|

|

указанному в регистрах Н и L |

|

|

ANA г |

Поразрядное И над содержимым регистра г 1 Z , S, Р, С = 0, АС = 0 |

4 |

|

|

и аккумулятора |

|

|

ANAM |

Поразрядное И над содержимым аккумуля- 1 Z , S, Р, С = 0, АС = 0 |

7 |

|

|

тора и ячейки памяти по адресу, указанному |

|

|

|

в регистрах Н и L |

|

|

XRAr |

Поразрядное ИСКЛЮЧАЮЩЕЕ ИЛИ над со- 1 Z, S, Р, С = 0, АС = 0 |

4 |

|

|

держимым регистра г и аккумулятора |

|

|

XRAM |

Поразрядное ИСКЛЮЧАЮЩЕЕ ИЛИ над со- 1 Z, S, Р, С = 0, АС = 0 |

7 |

|

|

держимым аккумулятора и ячейки памяти |

|

|

|

по адресу, указанному в регистрах Н и L |

|

|

ORAr |

Поразрядное ИЛИ над содержимым регист- 1 Z,S,P,C = 0, AC = 0 |

4 |

|

|

pa r и аккумулятора |

|

|

ORAM |

Поразрядное ИЛИ над содержимым аккуму- 1 Z, S, Р, С = 0, АС = 0 |

7 |

|

|

лятора и ячейки памяти по адресу, указанно- |

|

|

|

му в регистрах Н и L |

|

|

CMP г |

Сравнение содержимого регистра г и аккуму- 1 (Z, S, P, С, АС)3 |

4 |

|

|

лятора |

|

|

CMPM |

Сравнение содержимого аккумулятора и ячей- 1 (Z, S, P, С, АС)3 |

7 |

|

|

ки памяти по адресу, указанному в регист- |

|

|

|

рах Н и L |

|

|

INXrp |

Увеличение на единицу содержимого пары ре- 1 - |

5 |

|

|

гистров гр (В, D, Н, SP) |

|

|

DCXrp |

Уменьшение на единицу содержимого пары 1 - |

5 |

|

|

регистров гр (В, D, H, SP) |

|

|

DADrp |

Сложение содержимого пары регистров тр 1 С |

10 |

|

|

(В, D, H, SP) с содержимым пары регистров |

|

|

|

Н и L и хранение результата в Н и L |

|

|

POPrp |

Выдача данных из стека в пару регистров гр 1 (Z, S, P, С, АС)6 |

10 |

|

|

(В, D, H) или в аккумулятор и регистр при- |

|

|

|

знаков PSW |

|

|

PUSH rp |

Занесение в стек содержимого пары регист- 1 - |

11 |

|

|

ров гр (В, D, H) или содержимого аккумуля- |

|

|

|

тора и регистра признаков PSW |

|

|

STAXrp |

Запись содержимого аккумулятора в ячейку 1 - |

7 |

|

|

памяти, косвенно адресуемую парой регист- |

|

|

|

ров гр (В, D) |

|

|

LDAX rp |

Запись в аккумулятор содержимого ячейки 1 |

7 |

|

|

памяти, косвенно адресуемой парой регист- |

|

|

|

ров гр (В, D) |

|

|

RNZ |

Возврат из подпрограммы при отсутствии 1 - |

5/11 |

|

|

нуля (флаг нуля в состоянии 0) |

|

|

RZ |

Возврат из подпрограммы при наличии нуля 1 - |

5/11 |

|

|

(флаг нуля в состоянии 1) |

|

|

RNC |

Возврат из подпрограммы при отсутствии 1 - |

5/11 |

|

|

переноса (флаг переноса в состоянии 0) |

|

|

RC |

Возврат из подпрограммы при наличии пе- 1 - |

5/11 |

|

|

реноса (флаг переноса в состоянии 1) |

|

Продолжение прилож. 1

|

Мнемокод команды |

Описание команды |

Длина команды, Изменяемые флаги байт |

Число тактов |

|||

|

RPO |

Возврат из подпрограммы при отсутствии |

1 |

5/11 |

|||

|

|

четности (флаг четности в состоянии 0) |

|

|

|||

|

RPE |

Возврат из подпрограммы при наличии чет- |

1 |

|

|||

|

|

ности (флаг четности в состоянии 1) |

|

|

|||

|

RP |

Возврат из подпрограммы при положительном |

1 |

5/11 |

|||

|

|

результате (флаг знака в состоянии 0) |

|

|

|||

|

RM |

Возврат из подпрограммы при отрицательном |

1 |

5/11 |

|||

|

|

результате (флаг знака в состоянии 1) |

|

|

|||

|

RET |

Безусловный возврат из подпрограммы |

1 С4

|

5/11 |

|||

|

RLC |

Циклический сдвиг содержимого аккумуля- |

1 С4 |

|

|||

|

|

тора влево |

1 С4 |

|

|||

|

RRC |

Циклический сдвиг содержимого аккумуля- |

1 С |

|

|||

|

|

тора вправо |

|

|

|||

|

RAL |

Циклический сдвиг содержимого аккумуля- |

1 С4 |

|

|||

|

|

тора влево, включая флаг переноса |

1 С4 |

|

|||

|

RAR |

Циклический сдвиг содержимого аккумуля- |

1 С4 |

|

|||

|

|

тора вправо, включая флаг переноса |

|

|

|||

|

XCHG |

Обмен данными между парами регистров Н, |

1 |

4 |

|||

|

|

L HD.E |

|

|

|||

|

XTHL |

Обмен данными между двумя верхними ячей- |

1 |

18 |

|||

|

|

ками стека и парой регистров Н, L (сначала |

|

|

|||

|

|

самая верхняя обменивается с L , затем сле- |

|

|

|||

|

|

дующая с Н) |

|

|

|||

|

SPHL |

Передача в указатель стека содержимого ре- |

1 |

|

|||

|

|

гистров Н и L |

|

|

|||

|

PCHL |

Передача в счетчик команд содержимого пары 1 - |

5 |

||||

|

|

регистров Н и L с последующим выполнением |

|

||||

|

|

программы с адреса, равного новому содер- |

|

||||

|

|

жимому счетчика команд (по существу коман- |

|

||||

|

|

да перехода) |

|

||||

|

HLT |

Останов программы 1 - |

7 |

||||

|

NOP |

Отсутствие операции 1 - |

4 |

||||

|

DI |

Запрет на прерывание программы 1 - |

4 |

||||

|

EI |

Разрешение прервать программу 1 - |

4 |

||||

|

DAA |

Перевод двоичного представления содержимо- 1 — |

4 |

||||

|

|

го аккумулятора в двоично-десятичный код |

|

||||

|

СМА |

Поразрядное инвертирование содержимого 1 - |

4 |

||||

|

|

аккумулятора |

|

||||

|

STC |

Установка флага переноса С в единицу 1 С = 1 |

4 |

||||

|

CMC |

Инвертирование значения флага переноса 1 С=С |

4 |

||||

|

RSTA |

Повторный запуск программы с адреса 1 - |

11 |

||||

|

|

8А10 = (ОА08) |

|

||||

|

ADI<B2> |

Сложение содержимого байта В2 с содержи- 2 Z,S,P, С, АС |

7 |

||||

|

|

мым аккумулятора |

|

||||

|

ACI <В2> |

Сложение с учетом переноса содержимого 2 Z,S, P, С, АС |

7 |

||||

|

|

байта В2 с содержимым аккумулятора |

|

||||

|

SUI <В2> |

Вычитание содержимого байта В2 из содер- 2 Z, S, Р, С1 , АС2 |

7 |

||||

|

|

жимого аккумулятора |

|

||||

|

SBI <В2> |

Вычитание с заемом содержимого байта В2 2 Z, S, Р, С1 , АС2 |

7 |

||||

|

ANI <В2> |

из содержимого аккумулятора Поразрядное И над содержимым байта В2 и 2 Z , S, Р, С = 0, АС = 0 |

7 |

||||

|

|

содержимым аккумулятора |

|

||||

|

XRI <B2> |

Поразрядное ИСКЛЮЧАЮЩЕЕ ИЛИ над со- 2 Z, S, Р, С = 0, АС =0 |

7 |

||||

|

|

держимым байта В2 и содержимым аккуму- |

|

||||

|

|

лятора |

|

||||

Продолжение прилож. 1

|

Мнемокод команды |

Описание команды |

Длина команды, байт |

Изменяемые флаги |

Число тактов |

|

ORI<B2> |

Поразрядное ИЛИ над содержимым байта В2 |

2 |

Z,S,P, C = 0, AС=0 |

7 |

|

|

и содержимым аккумулятора |

|

|

|

|

CPI <В2> |

Сравнение содержимого байта В2 с содержи- |

2 |

(Z, S, Р,С, АС)3 |

7 |

|

|

мым аккумулятора |

|

|

|

|

IN <B2> |

Ввод данных в аккумулятор из порта ввода, |

2 |

- |

10 |

|

|

определяемого адресом в байте В2 |

|

|

|

|

OUT<B2> |

Вывод данных из аккумулятора в порт вы- |

2 |

- |

10 |

|

|

вода, определяемый адресом в байте В2 |

|

|

|

|

MVI r <B2> |

Занесение содержимого байта В2 в регистр г |

2 |

- |

7 |

|

MVI M <B2> |

Запись содержимого байта В2 в ячейку памя- |

2 |

- |

7 |

|

JNZ<B2><B3> |

ти по адресу, указанному в регистрах Н и L Переход в программе к выполнению команды по адресу в В2, ВЗ при отсутствии нуля (флаг нуля в состоянии 0) |

3 |

- |

10 |

|

JZ<B2><B3> |

Переход в программе к выполнению команды по адресу в В2, ВЗ при наличии нуля (флаг нуля в состоянии 1) |

3 |

- |

10 |

|

JNC<B2><B3> JC<B2><B3> |

Переход в программе к выполнению команды по адресу в В2, ВЗ при отсутствии переноса (флаг переноса в состоянии 0) Переход в программе к выполнению команды по адресу в В2, ВЗ при наличии переноса (флаг переноса в состоянии 1) |

3 3 |

- |

10 10 |

|

JPO<B2><B3> |

Переход в программе к выполнению команды по адресу в В2, ВЗ при наличии нечетности (флаг четности в состоянии 0) |

3 |

- |

10 |

|

JPE<B2><B3> |

Переход в программе к выполнению команды |

3 |

— |

10 |

|

|

по адресу в В2, ВЗ при наличии четности (флаг четности в состоянии 1) |

|

|

|

|

JP<B2><B3> |

Переход в программе к выполнению команды по адресу в В2, ВЗ при положительном результате (флаг знака в состоянии 0) |

3 |

|

10 |

|

JM<B2><B3> |

Переход в программе к выполнению команды по адресу в В2, ВЗ при отрицательном результате (флаг знака в состоянии 1) |

3 |

|

10 |

|

JMP<B2><B3> |

Безусловный переход к команде по адресу в В2, ВЗ |

3 |

— |

10 . с |

|

CNZ<B2><B3> |

Вызов подпрограммы при отсутствии нуля (флаг нуля в состоянии 0) |

3 |

|

11/175 с |

|

CZ<B2><B3> |

Вызов подпрограммы при наличии нуля (флаг нуля в состоянии 1) |

• 3 |

~ |

11/175 с |

|

CNC<B2><B3> |

Вызов подпрограммы при отсутствии перенос, (флаг переноса в состоянии 0) |

i3 |

— |

И/175 |

|

CC<B2><B3> |

Вызов подпрограммы при наличии переноса (флаг переноса в состоянии 1) |

3 |

— |

И/175 |

|

CPO<B2><B3> |

Вызов подпрограммы при наличии нечетности (флаг четности в состоянии 0) |

3 |

— |

11/175 |

|

CPE<B2><B3> |

Вызов подпрограммы при наличии четности (флаг четности в состоянии 1) |

3 |

— |

И/175 |

|

CP<B2><B3> |

Вызов подпрограммы при наличии положительного результата (флаг знака в состоянии 0) |

3 |

|

И/175 |

|

CM<B2><B3> |

Вызов подпрограммы при наличии отрицательного результата (флаг знака в состоянии 1) |

3 |

|

И/175 |

Продолжение прилож. 1

|

Мнемокод команды |

Длина Описание команды команды, Изменяемые флаги байт |

Число тактов |

|

CALL<B2><B3> |

Вызов подпрограммы из памяти по адресу, 3 - |

17 |

|

|

указанному в байтах В2, ВЗ |

|

|

LXIrp<B2><B3> |

Занесение содержимого двух байтов В2, ВЗ 3 - |

10 |

|

|

в пару регистров гр (В, D, Н, SP) |

|

|

STA<B2><B3> |

Запись содержимого аккумулятора в ячейку 3 - |

13 |

|

|

памяти по адресу в В2, ВЗ |

|

|

LDA<B2><B3> |

Запись в аккумулятор содержимого ячейки 3 — |

13 |

|

|

памяти по адресу в В2, ВЗ |

|

|

SHLD<B2><B3> |

Занесение содержимого регистров Н и L в па- 3 - |

16 |

|

|

мять: содержимое L пересылается в ячейку |

|

|

|

по адресу в В 2, ВЗ; содержимое регистра Н - |

|

|

|

в ячейку, адрес которой на единицу больше |

|

|

LHLD<B2><B3> |

Загрузка в регистры Н и L содержимого ячеек 3 - |

16 |

|

|

памяти: в L пересылаются данные из ячейки па- |

|

|

|

мяти по адресу в В2, ВЗ; в Н — из ячейки, ад- |

|

|

|

рес которой на единицу больше |

|

1. Флаг устанавливается при наличии заема в старший разряд, в противном случае сбрасывается.

2. Флаг устанавливается при наличии заема из старших четырех разрядов в младшие, в противном случае сбрасывается.

3. Флаг нуля Z устанавливается, если содержимое регистра или байта данных совпадает с содержимым аккумулятора; флаги знака и переноса S и С устанавливаются, если содержимое регистра или байта данных больше содержимого аккумулятора; флаг вспомогательного переноса АС устанавливается, если содержимое младших четырех разрядов регистра или байта данных больше содержимого соответствующих разрядов аккумулятора; флаг четности Р устанавливается, если байт разности между содержимым аккумулятора и содержимым регистра или байта данных содержит четное число единиц.

4. Состояние флага равно значению выдвигаемого из аккумулятора двоичного разряда.

5. Большее значение ( за косой чертой) указывает на число тактов при выполнении условий, меньшее — при невыполнении.

6. По команде POP PSW флаги устанавливаются в соответствии со значением разрядов слова, хранящегося в стеке; при выдаче данных из стека в другие регистры флаги не меняются.

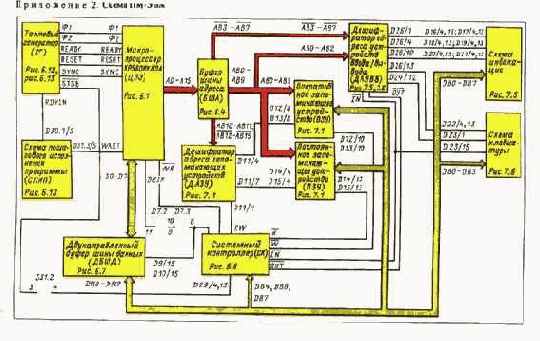

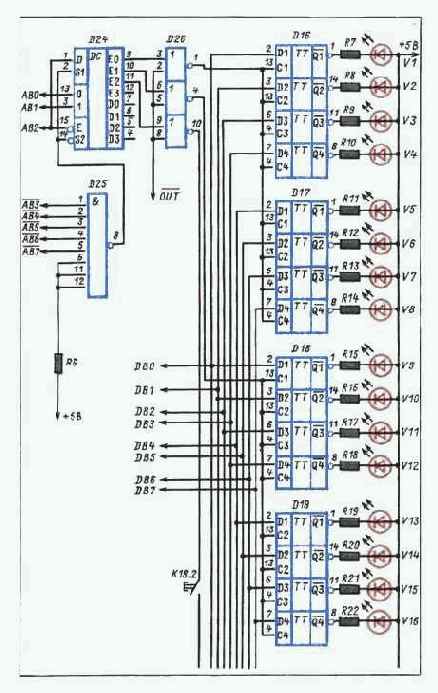

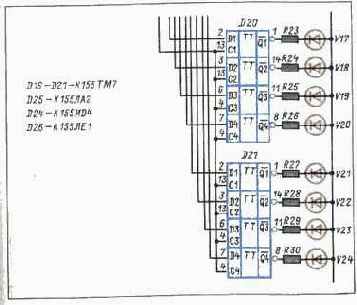

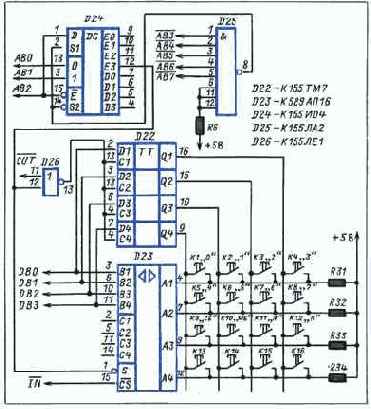

Приложение 2. СХЕМА ПМ-ЭВМ

Приложение 3. Таблица элементов, используемых в схеме ПМ-ЭВМ

|

Обозначение микросхемы |

Тип микросхемы |

Выводы микросхем |

|

Питание |

||

|

+ 5 В общее |

||

|

D1 |

КР580ИК80А |

Данные в тексте |

|

D2 |

КР580ГФ24 |

Данные в тексте |

|

D3-D7, D31 |

К155ЛН1 |

14 7 |

|

D8 |

К155ЛА1 |

14 7 |

|

D9, DIG, D23 |

К589АП16 |

16 8 |

|

Dll, D24 |

К155ИД4 |

14 7 |

|

D12, D13 |

КР541РУ2 |

18 9 |

|

D14, D15 |

КР556РТ4 |

16 8 |

|

D16-D22, D29 |

К155ТМ7 |

5 12 |

|

D25 |

К155ЛА2 |

14 7 |

|

D26 |

К155ЛЕ1 |

14 7 |

|

D27, D28 |

К155ЛАЗ |

14 7 |

|

D30 |

К155ТМ2 |

14 7 |

KB - 9 МГц

С1 - 0,15 мкФ

R1-R6 - 1 кОм

R7 — R30 — в зависимости от типа VI — V24

R31-R34- 5,1 кОм

V1-V24 - АЛ102А, АЛ102Г, АЛ112А-М

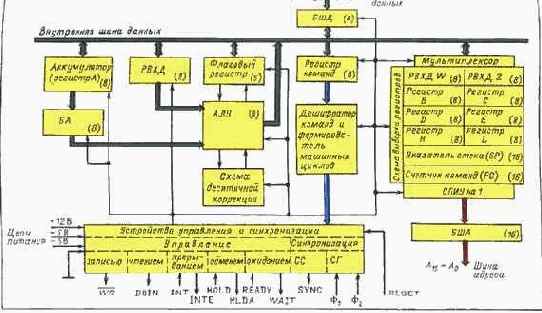

ФУНКЦИОНАЛЬНАЯ СХЕМА МИКРОПРОЦЕССОРА

При работе с ПМ-ЭВМ пользователю необходимо иметь информацию о числе и назначении всех регистров, специальных указателей, называемых флагами, и о системе команд МП. Число, назначение регистров, флагов и команд пользователь изменить не может. Он может изменять лишь содержимое регистров и использовать команды в любой нужной ему комбинации.

Как уже говорилось, под регистром подразумевается специальное запоминающее устройство, состоящее из элементов (триггеров) с двумя устойчивыми состояниями. Число элементов (восемь) соответствует одному байту. Большинство регистров микропроцессора 8-разрядные и лишь некоторые 16-разрядные. Все регистры разбиты на группы и отличаются различным функциональным назначением.

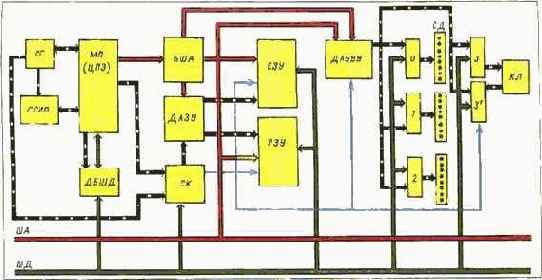

Основными блоками МП (рис. 4.4) являются: блок регистров общего назначения со схемой выборки регистров, регистр команд с дешифратором команд и формирователем машинных циклов, арифметическо-логическое устройство (АЛУ) с регистром А (аккумулятором), выполняющее арифметические и логические операции, регистр временного хранения данных W и Z (РВХД), флаговый регистр, устройство управления и синхронизации, буферы шины данных (БШД) и адреса (БША), буфер аккумулятора (БА), схема приращения и уменьшения (СПИУ).

Рис. 4.4. Схема ЦПЭ на базе микропроцессора КР580ИК80А:

СГ - сигналы генератора тактовых импульсов; СС — сигнапы синхронизации

Доступными программисту являются следующие регистры: шесть 8-разрядных регистров, адресуемых по одному или парами (регистры В, С, D, E, H, L); один 8-разрядный регистр А, называемый аккумулятором; один 16-разрядный регистр, называемый указателем стека; один 16-разрядный регистр, называемый счетчиком команд, или программным счетчиком.

В некоторых специальных случаях могут быть доступными данные следующих двух регистров: регистра команд (8-разрядного) ; флагового регистра (5-разрядного).

Программно недоступными пользователю являются регистры W и Z. Они используются для временного хранения данных при выполнении команд микропроцессором.

Регистры общего назначения. Эти регистры размерностью в один байт обозначаются В, С, D, E, H, L. Они используются для хранения данных и промежуточных результатов вычислений, выполняемых с помощью арифметическо-логиче-ского устройства. При обработке 16-разрядных слов возможно обращение к парам регистров (В, С); (D, E); (H, L).

Аккумулятор — специальный однобайтовый регистр, обозначаемый А. При выполнении арифметических и логических операций служит источником одного из операндов и местом запоминания результата выполнения операции. Аккумулятор является основным операционным звеном арифметическо-логического устройства. Он служит также местом хранения данных и результатов операций, выполняемых в АЛУ.

Регистр команд — однобайтовый регистр, в котором хранится код выполняемой команды. Этот регистр непосредственно пользователю недоступен. Это означает, что не существует команды, которая бы явным образом могла изменить его содержимое. После выполнения очередной команды в регистр команд автоматически записывается код следующей команды из ячейки оперативной памяти, адрес которой содержится в счетчике команд.

Счетчик команд — двухбайтовый (16-разрядный) регистр, обозначаемый PC, или программный счетчик. Этот регистр хранит адрес следующей команды, которая должна быть выполнена вслед за предыдущей. Счетчик команд автоматически получает приращение хранимого в нем адреса в зависимости от того, какую по длительности команду (в один, два или три байта) микропроцессор считывает из памяти, указывая всегда на 1-й байт следующей команды. На содержимое этого регистра пользователь может повлиять только с помощью команд, изменяющих последовательное выполнение программы (например, команд безусловного перехода), а также с помощью некоторых специальных команд.

Указатель стека-двухбайтовый (16-разрядный) регистр, обозначаемый SP. Этот регистр хранит адрес очередной ячейки стека. Стеком называется особым образом организованный участок оперативной памяти, выделяемый программистом для временного хранения содержимого внутренних регистров МП со специальным режимом доступа.

Эта область оперативной памяти необходима в том случае, когда нужно прекратить выполнение реализуемой последовательности команд и вернуться к ней позже, например для немедленного выполнения специальной подпрограммы или в результате прерывания программы. Данные от МП поступают в верхнюю часть стековой памяти, и при этом содержимое указателя стека уменьшается на единицу, чтобы всегда указывать на адрес последней заполненной ячейки стека (дно свободного пространства стека). Когда же данные выбираются (считываются) из стека, содержимое указателя стека увеличивается на единицу с каждым выбранным байтом. Эти операции со стеком называются стековыми. С их помощью легко организуются многоуровневые (вложенные) прерывания и программы обращения к подпрограммам из подпрограмм (к вложенным подпрограммам).

Флаговый регистр- регистр, содержащий 5 двоичных разрядов, называемых флагами, по числу хранимых в нем специальных признаков результатов некоторых операций. Иногда он называется регистром признаков или флаговым регистром битов условий. Значение флага указывает на результат выполнения какой-либо операции. Микропроцессор КР580ИК80А содержит флаговый регистр, состоящий из следующих флагов: флага нуля (Z - zero), флага переноса (С -carry), флага знака (S - sign), флага четности (Р -parity), флага дополнительного переноса (АС - auxiliary carry). Флаги всегда устанавливаются или сбрасываются автоматически после выполнения очередной команды, влияющей на флаги, в зависимости от результата операции. При этом флаг считается установленным, если флаговый разряд принимает значение 1, и сброшенным, если значение разряда 0. Состояния флагов используются в командах условного перехода. Результаты выполнения арифметических и логических операций над содержимым аккумулятора, регистров общего назначения или содержимым ячеек памяти оказывают влияние на флаги следующим образом.

Флаг нуля устанавливается в состояние 1, если после выполнения какой-либо команды получен нулевой результат, и сбрасывается в 0 в случае ненулевого результата.

Флаг переноса устанавливается в 1, если в результате операций сложения и сдвига появляется единица переноса из старшего разряда байта данных, а также если появляется заем из старшего разряда после выполнения операций вычитания или сравнения, в противном случае флаг сбрасывается в 0.

Флаг знака устанавливается в 1, если в результате выполнения операций появляется логическая единица в старшем разряде байта данных (указание на отрицательный результат), и сбрасывается в 0 в случае нулевого значения старшего разряда (указание на положительный результат).

Флаг четности устанавливается в 1, если после выполнения операций сумма единиц в байте данных, подсчитываемых с помощью операции сложения по модулю 2, четна (значение суммы по модулю 2 равно 0), и сбрасывается в 0 в противном случае (число единиц — нечетное).

Флаг дополнительного переноса устанавливается в 1, если в результате выполнения команды появляется сигнал переноса из третьего разряда в четвертый в байте данных результата. Если такого переноса нет, флаг дополнительного переноса сбрасывается в 0. Сигнал этого флага используется во многих схемах вычислений, однако он особенно необходим при сложении чисел в двоично-десятичной форме.

Перейдем теперь к рассмотрению того, как микропроцессор выполняет команды.

ГРУППА АРИФМЕТИЧЕСКИХ КОМАНД

Команды этой группы предназначены для выполнения арифметических операций над данными, хранимыми в регистрах и ячейках памяти. Эти команды в отличие от команд предыдущей группы, как правило, оказывают влияние на значения разрядов флагового регистра, поскольку при выполнении арифметических операций меняются знаки используемых чисел, возникают сигналы переноса, появляются нулевые результаты и т. п. Рассмотрим примеры размещения в байтах некоторых команд этой группы.

Команда ADD r. Эта команда выполняет сложение содержимого регистра-источника S с содержимым аккумулятора А. Результат сложения помещается в аккумулятор. Чтобы получить конкретную команду, необходимо в формате команды вместо символов S проставить код регистра-источника из табл. 4.4. Например, команда 10 000 001 производит сложение содержимого регистра С с содержимым аккумулятора А. Двоичный код этой команды 10 000 001 В; в восьмеричной системе это число представляется кодом 201Q. Это представление является восьмеричным кодом команды ADD С, выполняющей указанное выше сложение (см. список команд в приложении 1). Размещение команды ADD г в байте приведено на рис. 4.9,д.

Команда SUB r. Команда выполняет вычитание содержимого регистра-источника S из содержимого аккумулятора. Результат заносится в аккумулятор (рис. 4.9,6). Например, команда 10 010 ОН В выполняет вычитание содержимого регистра Е из содержимого регистра А и помещает результат в аккумулятор. Код этой команды SUB Е — 223 Q.

ГРУППА КОМАНД ПЕРЕХОДОВ

Эта группа команд предназначена для организации правильной последовательности выполнения программы. Сюда входят команды безусловного и условного переходов, команды вызова подпрограммы и возвращения к главной программе. Все команды этой группы на флаги влияния не оказывают. Команды безусловного перехода выполняют специальные операции над содержимым счетчика команд. Команды условного перехода обеспечивают необходимое ветвление программы путем анализа состояния одного из четырех флагов: нуля, знака, четности и переноса, коды которых указаны в табл. 4.4.

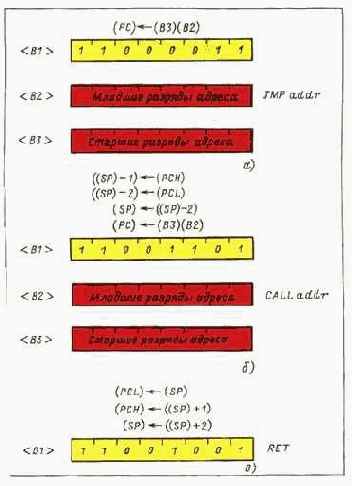

Команда JMP <В2> <ВЗ> — трехбайтовая команда передает управление команде по адресу, содержащемуся в третьем и втором байтах текущей команды. Это осуществляется путем записи содержимого третьего и второго байтов команды в счетчик команд (рис. 4.11,а). Как уже отмечалось в § 4.3, счетчик команд представляет собой 16-разрядный регистр, содержащий адрес, по которому можно обратиться для считывания очередного байта команды. Восьмеричный код этой команды - 303 Q.

Команды CALL и RET — команды безусловного перехода. Первая из них передает управление подпрограмме, прекращая выполнение основной программы; вторая передает управление главной программе, возвращаясь к ее выполнению (рис. 4.11,£, в). Первая команда — трехбайтовая. Восемь старших разрядов адреса следующей команды пересылаются в ячейку памяти, адрес которой на единицу меньше содержимого указателя стека. Восемь младших разрядов адреса следующей команды пересылаются в ячейку памяти, адрес которой на две единицы меньше содержимого указателя стека. Содержимое указателя стека уменьшается на две единицы. Управление передается команде, адрес которой размещается в третьем и втором байтах команды CALL

Рис. 4.11. Примеры размещения некоторых команд переходов в байтах

Команда RET — однобайтовая. Ее восьмеричный код — 311Q (код предыдущей команды CALL — 315Q). В процессе выполнения этой команды содержимое указателя стека получает приращение на две единицы.

Содержимое ячейки памяти по адресу, хранящемуся в указателе стека, пересылается в счетчик команд на место младших восьми разрядов. Содержимое ячейки памяти по адресу, на единицу большему, чем содержимое указателя стека, пересылается в счетчик команд на место старших восьми разрядов. Таким образом, возвращение к главной программе происходит всегда путем обращения к байту команды, непосредственно следующему за байтом, используемым командой CALL

4.6.5. ГРУППА КОМАНД УПРАВЛЕНИЯ И РАБОТЫ СО СТЕКОМ

Команды этой группы предназначены для управления работой микропроцессора, устройствами ввода/вывода и стеком. Команды этой группы не оказывают влияния на флаги. Рассмотрим в качестве примера работу некоторых команд из этой группы.

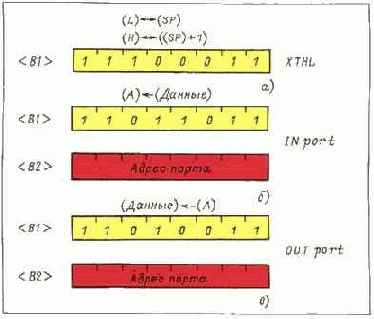

Команда XTHL — однобайтовая команда с восьмеричным номером 343Q. Является примером наиболее длинных по времени исполнения команд - занимает 18 машинных тактов.

В процессе выполнения команды содержимое регистра L меняется на содержимое ячейки памяти по адресу, содержащемуся в указателе стека, и наоборот. Содержимое регистра Н меняется на содержимое ячейки памяти по адресу, на единицу большему, чем содержимое указателя стека, и наоборот (рис. 4.12,я). На это уходит пять машинных циклов.

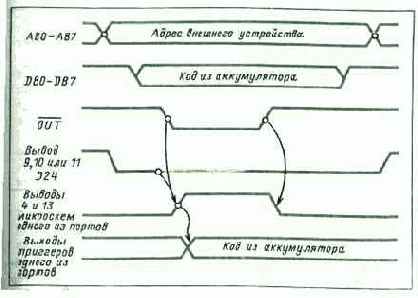

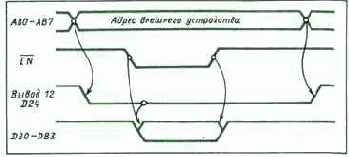

Команды IN <B2>, OUT <B2> . Эти команды предназначены для ввода данных от входного порта в аккумулятор и вывода данных из аккумулятора в выходной порт соответственно. Первая команда имеет восьмеричный код 333 Q, вторая — 323 Q. Обе команды — двухбайтовые. Второй байт обеих команд отведен под адрес соответствующего входного и выходного портов. В результате выполнения первой команды данные от входного порта по двунаправленной шине данных передаются в аккумулятор. В результате выполнения второй команды данные выводятся по той же шине данных из аккумулятора в выходной порт (рис. 4.12,6, в).

Рис. 4.12. Примеры размещения некоторых команд управления в байтах

На этом закончим рассмотрение примеров размещения в байтах команд описанных выше групп и перейдем к вопросу о том, как составляется программа решения на ПМ-ЭВМ задачи с использованием приведенного в приложении 1 списка команд.

ГРУППА ЛОГИЧЕСКИХ КОМАНД

Команды этой группы предназначены для выполнения логических, или булевых, операций над данными, .содержащимися в регистрах, ячейках памяти, а также над флагами условий. К этим операциям относятся операции: логического сложения (ИЛИ), логического умножения (И), суммирования по модулю 2, сравнения, сдвига, дополнения до 1 и до 2. Как и команды предыдущей группы, все логические команды оказывают влияние на флаги.

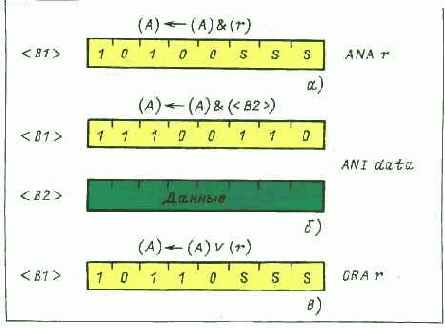

Команда ANA г выполняет параллельно поразрядное логическое И над содержимым регистра-источника и аккумулятора. Результат операции заносится в аккумулятор (рис. 4.10,а). Например, команда 10 100 100 В выполняет операцию логического умножения поразрядно над содержимым регистра Н и А и заносит результат в аккумулятор. Двоичный код 10 100 100 В соответствует восьмеричному коду 244Q команды ANA H.

Рис. 4.10. Примеры размещения некоторых логических команд в байтах

Команда ANI < В2 > является двухбайтовой и также выполняет поразрядную операцию логического И, но над содержимым второго байта команды и аккумулятора. Команда имеет восьмеричный код-3460 (рис. 4.10,6). Результат операции заносится в аккумулятор.

Команда ORAr аналогична команде ANA r, но в отличие от нее выполняет операцию поразрядного логического ИЛИ. Результат операции заносится в аккумулятор (рис. 4.10,в).

И ОБЛАСТИ ИХ ПРИМЕНЕНИЯ

Понятие микро-ЭВМ отнюдь не означает, что пользователь имеет дело с упрощенным вариантом обычной ЭВМ, обладающим весьма ограниченными возможностями В истории создания вычислительных машин десятилетие с 70-х по 80-е годы сыграло важную роль. Благодаря успехам микроэлектронной технологии появилась возможность конструировать вычислительные машины небольших габаритов, с малым потреблением электроэнергии и в достаточной мере "производительные". Вычислительные возможности современных микро-ЭВМ не уступают возможностям средних ЭВМ начала 70-х годов. Если понятие ЭВМ неразрывно связано с понятием вычислительного центра, крупного предприятия или сложной технической системы, то микро-ЭВМ - это массовое изделие, доступное не только небольшим производственным коллективам но и отдельным лицам вследствие невысокой стоимости, малой материалоемкости, низкого энергопотребления, высокой надежности. Микро-ЭВМ может быть использована для управления производством, а также отдельной, в ряде случаев сложной технической системы, как элемент оборудования рабочего места конструктора-исследователя или научного работника, в быту и во многих других сферах.

Переворот в технике конструирования ЭВМ произошел вследствие перехода к изготовлению основных узлов вычислительной машины (и в частности, ее главного узла - центрального процессорного элемента) в габаритах одной микросхемы или нескольких микросхем с площадью размещения активных элементов в каждой микросхеме порядка 100 мм2 и менее. При разработке такого процессора, получившего название "микропроцессор" (МП), было учтено требование максимального использования аппаратурных возможностей выполнения им вычислительных или логических функций.

В конструктивном отношении микропроцессоры могут быть однокристальными (выполненными в виде одной микросхемы), многокристальными (выполненными в виде нескольких разнотипных микросхем, каждая из которых представляет собой функционально законченную часть логической схемы процессора) и секционными многокристальными (выполненными в виде нескольких однотипных микросхем, представляющих собой отдельные секции, позволяющие построить процессор с числом разрядов, пропорциональным числу используемых секций).

Кроме МП, предназначенных для обработки дискретной информации, существуют аналоговые микропроцессоры (АМП), предназначенные для обработки аналоговой информации. В их структуру включены аналого-цифровые (аналого-дискретные) и цифро-аналоговые (дискретно-аналоговые) преобразователи, т. е. устройства, преобразующие аналоговый сигнал (например, непрерывно меняющееся входное напряжение) в цифровой (набор напряжений двух фиксированных уровней, представляющих двоичный код) и обратно. Обработка аналоговой информации, преобразованной в дискретную, производится в АМП, как и в обычном микропроцессоре. Кроме однокристальных микропроцессоров существуют однокристальные микро-ЭВМ (ОМ-ЭВМ), представляющие собой микросхему, объединяющую в своем составе все основные устройства, необходимые для ее функционирования.

При использовании ОМ-ЭВМ необходимо добавить источник питания, внешние устройства и в ряде случаев дополнительное внешнее запоминающее устройство. На базе МП или ОМ-ЭВМ может быть построена одноплатная микро-ЭВМ, представляющая собой законченный конструктивный элемент. Одноплатная микро-ЭВМ может входить в состав многоплатной микро-ЭВМ, включающей, кроме того, платы сопряжения с внешними устройствами, а также источник питания, пульт управления, аппаратуру индикации ("голая микро-ЭВМ"). Если "голую микро-ЭВМ" "одеть" внешними устройствами (алфавитно-цифровой клавиатурой, дисплеем, накопителем на гибком магнитном диске и т. п.), то получится вычислительный комплекс.

Одноплатная микро-ЭВМ, ОМ-ЭВМ и "голая микро-ЭВМ" могут быть использованы в составе управляющих систем или измерительных комплексов. Примерами ОМ-ЭВМ являются однокристальные восьмиразрядные микро-ЭВМ серии К 1816, однокристальные четырехразрядные микро-ЭВМ серий К 1820 и К 1814. К одноплатным машинам относится, например, микро-ЭВМ "Истра", а к многоплатным — микро-ЭВМ "Электроника 60", ЕС-1840, "Квант" и др.

По способу реализации системы команд микро-ЭВМ разделяются на два типа. В микро-ЭВМ первого типа система команд является постоянной (фиксированной), а в микро-ЭВМ второго типа - изменяемой (программируемой на уровне микрокоманд). Более простыми, дешевыми и распространенными являются машины первого типа.

К наиболее распространенным микро-ЭВМ, выпускаемым отечественной промышленностью, относятся персональные (ПЭВМ) и профессиональные персональные (ППЭВМ) машины семейства "Электроника", а также машины: ЕС 1840, "Искра 1030", "Нейрон И9.66", "Агат", "Корвет", СМ-1810 и др.

Семейство микро-ЭВМ "Электроника" - это ряд универсальных программно-совместимых машин различной производительности. Наиболее производительные машины этого ряда сравнимы по параметрам с развитыми мини-ЭВМ. Семейство микро-ЭВМ "Электроника" - это ряд машин, ориентированных на использование в управлении технологическими процессами, для сбора и обработки данных, для обработки сообщений и управляющей информации в системах связи и контрольно-измерительных системах. Отдельные модели ряда могут быть встроены в соответствующие подсистемы управления и контроля Модели "Электроника" - это микро-ЭВМ универсального применения, которые с успехом могут быть использованы в системах автоматизированного управления. Одним из важнейших достоинств этой серии является программная совместимость с отечественными мини-ЭВМ СМ-3, СМ-4, а также с зарубежными мини-машинами семейства PDP-11, что позволяет использовать разработанное ранее программное обеспечение. Машины "Электроника 85" и "Электроника БК-0010" относятся к классу персональных компьютеров.

Предназначенная в основном для тех же целей микро-ЭВМ СМ-1810 является машиной, программно-совместимой с микро-ЭВМ, построенными на базе микропроцессора 8080 фирмы Intel.

Кроме перечисленных микро-ЭВМ отечественной промышленностью выпускается большой ассортимент диалоговых вычислительных комплексов, например ДВК-1 - ДВК-3, с высокой производительностью, что позволяет использовать программное обеспечение этой машины, а также программное обеспечение мини-ЭВМ "Электроника 100/25".

Операцион ная система вычислительного комплекса ДВК допускает использование языков БЕЙСИК, ФОРТРАН, ПАСКАЛЬ, КОБОЛ, ПЛ/1, что предоставляет большие возможности для программирования.

Современные микро-ЭВМ обладают несравненно большими возможностями, чем многие вычислительные машины прошлых поколений. Дешевизна, надежность и доступность микро-ЭВМ позволяют использовать их для решения таких задач, для которых применение средств вычислительной техники ранее было неоправданным.

В сфере промышленного производства микро-ЭВМ могут использоваться в составе информационно-управляющих вычислительных систем (ИУВС), в системах технического управления объектами и технологическими процессами и в системах организационно-технического управления цехами, предприятиями, отраслями и т. п. В таких системах микро-ЭВМ используются для сбора и обработки данных, выполнения сложных экономических и технических расчетов, планирования, управления и контроля. В управлении сложными техническими системами микро-ЭВМ чаще всего используются в составе встроенных средств управления и контроля. Замена высокопроизводительной и дорогостоящей ЭВМ, используемой в качестве центрального управляющего органа, сетью микро-ЭВМ повышает надежность, эффективность и гибкость управления сложной технической системой, позволяет организовать управление в реальном времени и снижает стоимость общих затрат на управление.

Применение микро-ЭВМ в машиностроении позволяет перейти от существующих конструкций станков с числовым программным управлением к более совершенным высокопроизводительным робототехническим конвейерным системам и к организации на их основе гибких автоматизированных производств.

Расширению сферы использования ЭВМ (особенно в последние годы) способствовало появление нового класса микро-ЭВМ — персональных ЭВМ (ПЭВМ). Под ПЭВМ подразумевается микро-ЭВМ, предназначенная для индивидуального пользования (подобно пишущей машинке, телевизору, магнитофону), но со значительно более широкими функциональными возможностями, позволяющими использовать ее для решения самых разнообразных задач — от сложнейших профессиональных расчетов до самых мелких бытовых.

Обычно ПЭВМ так и классифицируются: профессиональные и бытовые. Профессиональные ПЭВМ используются профессионалами-конструкторами, технологами, инженерами, научными работниками, журналистами, редакторами и т. п. Они оказываются полезными при индивидуальной обработке технической, экономической, медицинской и другой информации, в преподавательской деятельности; позволяют обеспечить оперативный доступ к отраслевым, региональным информационным источникам через локальные сети ЭВМ. Бытовые ПЭВМ могут быть использованы в качестве домашнего информационного центра. С их помощью можно проводить развлекательные и познавательные игры, организовывать учебные курсы (например, по изучению иностранных языков или курсов по школьной программе), обеспечивать доступ к справочной информации: адресам, телефонам, рецептам и т. п. Микро-ЭВМ, выпускаемые промышленностью, являются слишком сложными, чтобы брать их за образец при попытке самостоятельного построения. Возникает вопрос, можно ли вообще самому построить хоть какой-нибудь простейший вариант вычислительной машины?

И ОБРАБОТКА ДАННЫХ

Системы сбора и обработки данных, как правило, являются частью иерархических систем управления или коммуникации и предназначены для приема данных, представленных в виде аналоговых или цифровых сигналов различных уровней и форматов, преобразования их в стандартную цифровую форму, обработки в соответствии с заданным алгоритмом и выдачи обработанных данных на индикационные устройства или в старшую иерархическую ступень системы.

В качестве примера системы сбора и обработки данных рассмотрим конструирование на базе ПМ-ЭВМ счетчика случайных событий. Введем в ПМ-ЭВМ программу

014 000 006 MVI В, OOO.Q

014001 000

014002016 MVIC, OOOQ

014 003 000

014 004 026 MVI D, OOOQ

014 005 000

014006315 Ml: CALL SKL

014 007 177

014 010000

014 Oil 170 MOV А, В

014012074 INR A

014 013 047 DAA

014014323 OUT, OOOQ

014 015 000

014 016 107 MOV В, А

014017171 MOV А, С

014020316 ACI, 0000

014021 000

014 022 047 DAA

014023323 OUT. 0010

014024 001

014025 117 MOVC, A

014026 172 MOV A, D

014027316 ACI, OOOQ

014030000

014031 047 DAA

014032323 OUT, 002Q

014 033 002

014034127 MOVD. A

014035303 JMP, Ml

014 036 006

014037014

После ввода программы нажмем кнопки СБРОС и П. В портах 002, 001, 000 индицируются соответственно 006Q - код первой команды программы и 014Q OOOQ — ее адрес в памяти. Теперь будем нажимать любую кнопку клавиатуры (кроме кнопки СБРОС) - в портах 002, 001, 000 индицируется количество нажатий кнопки, выраженное в двоично-десятичном коде, начиная с 000 001D и кончая 999 999D. Для обнуления счетчика достаточно нажать кнопки СБРОС и П. Таким образом, чисто программным путем нами реализована простейшая система сбора и обработки информации, регистрирующая нажатия кнопок, подсчитывающая эти нажатия и выдающая на индикацию в двоично-десятичной форме число, равное количеству нажатий.

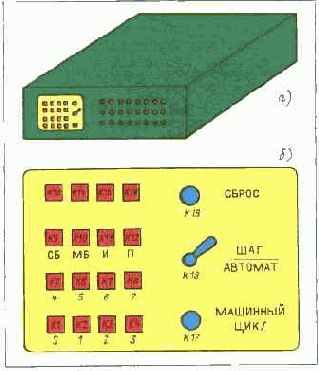

ИНСТРУКЦИЯ ПО РАБОТЕ НА МИКРО-ЭВМ

1. После включения микро-ЭВМ на индикаторах портов 002Q и 001Q высветится адрес младшей ячейки ОЗУ 00001100В и 00000000 В соответственно, а на индикаторах порта OOOQ высветится содержимое этой ячейки.

2. Для того чтобы посмотреть содержимое произвольной ячейки ОЗУ, необходимо:

а) набрать с помощью кнопок 0 — 7 на индикаторах порта OOOQ старший байт адреса этой ячейки и нажатием на кнопку СБ переслать его на индикаторы порта 002Q;

б) набрать с помощью кнопок 0 — 1 на индикаторах порта OOOQ младший байт адреса этой ячейки и нажатием на кнопку МБ переслать его на индикаторы порта 001Q. После этого на индикаторах порта OOOQ высветится содержимое необходимой ячейки.

3. Для того чтобы записать в произвольную ячейку необходимый код команды или данные, нужно:

а) выполнить п. 2 Инструкции;

б) набрать с помощью кнопок 0 — 7 необходимый код на индикаторах порта OOOQ. Этот код также попадет в регистр С;

в) нажать кнопку И, что вызовет запись кода в ячейку памяти и одновременно индикацию адреса и содержимого следующей ячейки.

4. Для того чтобы запустить программу, нужно:

а) записать ее в память (см. пп. 1, 2, 3 Инструкции) ;

б) набрать с помощью кнопок 0 — 7 старший байт адреса команды, с которой должно начаться выполнение программы на индикаторах порта OOOQ, и нажатием на кнопку СБ переслать его на индикаторы порта 002Q;

в) набрать с помощью кнопок 0 — 7 младший байт адреса команды, с которой должно начаться выполнение программы на индикаторах порта OOOQ, и нажатием на кнопку МБ переслать его на индикаторы порта 001Q;

г) запустить программу нажатием на кнопку 77.

5. Для того чтобы прервать выполнение программы, необходимо нажать на кнопку СБРОС.

ЭТАПЫ СБОРКИ И ПРОВЕРКИ УЗЛОВ

Читатель ознакомился с принципами работы микропроцессорной системы на базе МП типа КР580ИК80А, системой команд микропроцессора и схемой ПМ-ЭВМ, построенной на базе данного микропроцессора. Теперь ему предстоит собрать микро-ЭВМ и, используя простейшие средства отладки, довести ее до рабочего состояния.

Для сборки необходима плата, на которой будут располагаться микросхемы и другие элементы ПМ-ЭВМ. Плата изготовляется из стеклотекстолита или гетинакса толщиной 1,5 — 2,0 мм размером примерно 210x240 мм. В зависимости от имеющихся возможностей монтаж платы может быть выполнен по-разному.

Если плата не из фольгированного материала, то предварительно делается разметка на миллиметровке размещения деталей, затем миллиметровка наклеивается на плату и сверлятся отверстия под все выводы деталей. При небольших размерах платы микросхемы можно расположить перпендикулярно длинной стороне платы в два ряда, сделав пропилы тонкой ножовкой для выводов. В этом случае отпадает необходимость сверлить отверстия под каждый вывод. После отмывания миллиметровки детали устанавливаются на плате с одной стороны так, что их выводы попадают в просверленные отверстия и слегка отгибаются, препятствуя выпадению деталей. Микросхемы, пока они не подпаяны, требуют осторожного обращения ввиду опасности повреждения разрядом статического электричества. Берите их не за выводы, а за корпус!

Выводы деталей в соответствии с принципиальной схемой соединяются проводами путем пайки припоем ПОС-60 с жидким канифольным флюсом маломощным низковольтным паяльником, корпус которого подсоединен к заземлению через резистор сопротивлением несколько сотен килоом. Для монтажа можно использовать, например, провод МГТФ-0,05, зачищенный с концов на 5 мм с помощью кусачек, в которых сделаны специальные выемки глубиной около 0,5 мм.

Если для монтажа используется макетная плата с металлизированными отверстиями для выводов деталей и контактными площадками для подпайки соединительных проводов, то после размещения микросхем и других деталей на плате они подпаиваются с обратной стороны к плате, а затем соединяются проводами аналогично предыдущему.

От качества пайки существенным образом зависит надежность работы будущей ПМ-ЭВМ. Использование специально разработанной печатной платы облегчает последующие монтаж, отладку и повышает надежность работы устройства. Для ПМ-ЭВМ может быть использована как односторонняя, так и двухсторонняя плата. Если плата односторонняя, придется часть монтажа выполнить навесными проводниками. В двухсторонней плате, если сквозные отверстия, предназначенные для соединения печатных проводников с разных сторон платы, не металлизированы, в них необходимо вставить кусочки провода и пропаять с обеих сторон. Если нужно произвести изменения в плате с печатным монтажом, лишние соединения ликвидируются, для чего дважды разрезается печатный проводник острым ножом на расстоянии 1-2 мм и середина удаляется. Новые соединения можно сделать навесными проводниками. Монтаж каждого из блоков: микропроцессорного, памяти и устройств ввода/вывода - можно выполнить на отдельных платах, что в какой-то мере облегчает отладку. В конструкции, выполненной авторами, ПМ-ЭВМ размещена на плате с двухсторонним печатным монтажом. На торцевой стороне платы имеются два разъема. Через один разъем подключаются клавиатура и источники питания, а через другой выведены внутренние шины МП системы, что позволяет подключать различные расширяющие блоки.

Отладку ПМ-ЭВМ можно производить поэтапно по мере сборки В первую очередь необходимо собрать блок процессора (микросхемы D1-D7, D9, D10, D27, D28, D30, D31), причем для микросхемы D1 (микропроцессор) крайне желательно поставить панельку. Проверьте правильность монтажа, выньте микропроцессор из панельки и подайте питание. Проверьте тестером наличие питающих напряжений на выводах микросхем. При наличии осциллографа проверьте работу тактового генератора - на выводах 10 к 11 микросхемы D2 должны наблюдаться тактовые импульсы Ф2 и Ф1. Выключите питание и вставьте микропроцессор в панельку, подключите резисторы по 300 510 Ом между общим проводом и линиями шины данных DB7 — DBO.

Тем самым имитируется считывание команды NOP (код OOOQ). Поставьте переключатель К18 в положение АВТОМАТ, подайте питание и проверьте с помощью осцилло-графа наличие импульсов на линиях шины адреса АВ11 — АВО и АВ15-АВ12. Длительность импульсов (длительность уровня логического нуля или логической единицы) на линии АВО должна составить четыре тактовых интервала (машинный цикл команды NOP), т. е. 4 мкс. Длительность импульсов на следующих линиях шины адреса последовательно удваивается. Если на какой-либо линии нет импульсов, проверьте последовательнс прохождение сигнала от вывода МП до соответствующей линии. Если сигнала нет и на выводе МП, то можно предположить либо замыкание данной сигнальной линии на какой-либо постоянный уровень, либо неисправность МП по данному выводу. Если импульсов нет ни на одной из линий шины адреса и на соответствующих выводах МП, то, скорее всего, неисправен МП. Но к тогда прежде чем забраковать МП, сначала проверьте напряжения и сигналы на всех его выводах. Желательно проверить МП. вставив его в панельку заведомо исправной МП-системы. Если сигнал исчезает по пути от МП к адресной шине, нетрудно локализовать неисправность, которая может быть вызвана следующими причинами: ошибками в логической схеме, ошибками в монтаже, случайными замыканиями или обрывами проводящих линий, неисправностью соответствующих микросхем. Прежде чем выпаивать неисправнук микросхему, убедитесь еще раз, что других причин неисправности нет, так как замена микросхемы, особенно в печатной плате, — процесс весьмг трудоемкий. Если микросхема заведомо неисправна, проще всего ее извлечь, перекусив кусачками ножки. Затем уже можно извлечь по отдельности остатки каждой ножки с помощью пинцета и паяльника и прочистить отверстия с помощью заостренной спички или высверлить тонким сверлом. Извлечь микросхему без повреждения значительно сложнее. Для этого необходимо иметь либо паяльник с многими жалами или широким жалом, либо паяльник с отсосом.

После проверки шины адреса проверьте с помощью осциллографа выдачу сигнала R (чтение) на выводе 11 микросхемы D27 и сигнала RW (обращение к памяти) на выводе 3 микросхемы D28. Если сигналов нет, проверьте наличие сигналов DBIN на выводах 10 к 13 микросхемы D27, MR на выводе 12 микросхемы D27, STSTB на ножках 4 и 13 микросхемы D29 и соответствующего машинному циклу чтения команды управляющего слова (его код 242Q) на шине данных DBO-DB7, т. е. на выводах 3, 6, 10, 13 микросхемы D9 и 2, 3, 6, 7 микросхемы D29 соответственно. Если какого-либо сигнала нет, проверьте по цепочке логических схем последовательно, придя к выводам шины данных, DBIN и SYNC микропроцессора на выводах 10, 9, 8, 7, 3, 4, 5, 6, 17, 19 соответственно. Проверьте функционирование кнопки СБРОС. При ее нажатии МП не выдает никаких сигналов, при отпускании вновь появляются описанные выше сигналы.

Поставьте переключатель К18 в положение ШАГ, нажмите и отпустите кнопку СБРОС. Проверьте тестером или логическим пробником состояние шины адреса, на которой должен быть адрес 000Q 000Q, наличие сигналов R, DBIN и RW, а также наличие кода 000Q на шине данных МП. Нажимайте кнопку К17. При каждом нажатии кнопки на шине адреса должен появляться адрес, на единицу больший предыдущего, а состояние остальных контролируемых линий не должно изменяться. Если этого не происходит, проверьте исправность схемы шагового режима (микросхемы D3I.3, D31.4, D30).

После проверки микропроцессорного блока снимите питающие напряжения, отключите резисторы, временно подпаянные к шине данных, и соберите блок памяти, состоящий из микросхем D8, D11-D15, пока не подпаивая микросхемы ОЗУ (D12, D13). Подключите питание, поставьте переключатель К18 в положение ШАГ, нажмите и отпустите кнопку СБРОС. Начинается исполнение программы монитора в шаговом режиме по машинным циклам. Проследите с помощью тестера, проверяя коды на шине данных, исполнение команд монитора, начиная с команды JMP по адресу 000Q 000Q и кончая командой IN по адресу 000Q 203Q.

Если команды исполняются в соответствии с программой и в соответствующих местах программы вырабаты ваются сигналы R, W. IN и OUT, то можно приступить к следующему этапу изготовления и отладки ПМ-ЭВМ; если же нет, тс необходимо проверять: цепь прохождения кода считываемой команды до выводов шины данных МП, правильность дешифрации адреса по сигналам выборки памяти на выводах 8 микросхем D12, D13 и выводах 14 микросхем D14, D15, правильность выдачи управляющего слова по сочетанию на выходах микросхемы D29, наличие сигнала WR на выходе МП при исполнении машинных циклов записи в память и вывода.

Проверив работу микропроцессорного блока совместно с ПЗУ в шаговом режиме, отключите питание и соберите остальную часть схемы ПМ-ЭВМ, впаяв в том числе и микросхемы ОЗУ. Подайте питание, поставьте переключатель К18 в положение АВТОМАТ, нажмите и отпустите кнопку СБРОС. Если схема собрана правильно и все вновь включенные элементы исправны, то на индикаторах портов 001 и 000 высветится адрес начальной ячейки оперативной памяти 014Q OOOQ, а индикаторы порта 002 высветят содержимое этой ячейки. Проверьте работу клавиатуры, ее цифровой и функциональной частей. Если работа соответствует описанию, приведенному в гл. 7, то дальнейшие проверки будут чисто программными, например проверка ОЗУ. Если клавиатура функционирует неправильно, в целях проверки содержимого ПЗУ выясните, не работает ли клавиша просмотра памяти И. Переведите ПМ-ЭВМ в шаговый режим, нажмите и отпустите кнопку СБРОС и при последовательном исполнении команд монитора проследите прохождение всех сигналов. На каждом шаге порт 002 будет отображать информацию на шине данных, в то время как порты 001 и 000 будут отображать информацию, выдаваемую по командам OUT в соответствующие порты. В шаговом режиме затруднительно проверить правильность функционирования программы-монитора в той части, где анализируются коды нажатых клавиш, так как имеющееся в ней обращение к подпрограмме временной задержки занимает сотни машинных циклов и мало у кого хватит терпения дойти до конца.Если неисправность не удалось обнаружить и устранить, то необходимо собрать несложное устройство — статический аппаратный эмулятор, описываемый в § 8.2. Можно и начать с его сборки, прежде чем приступать к сборке и отладке ПМ-ЭВМ, и тем сберечь немало времени. В заключение еще раз напомним, что в процессе отладки микросхемы следует вставлять и вынимать только при выключенном питании и после каждой переделки, включив питание, следует прежде всего проверить, подается ли оно на все микросхемы.

КАК МИКРОПРОЦЕССОР ВЫПОЛНЯЕТ КОМАНДУ?

В ПМ-ЭВМ используется микропроцессор КР580ИК80А, структурная схема которого приведена на рис. 4.4. Микропроцессор содержит 16-разрядную шину адреса и 8-разрядную шину данных, способную к передаче сообщений в двух возможных направлениях. Единовременно передаваемая порция информации соответствует одному байту (8 двоичных разрядов). В самом общем случае возможны следующие передачи сообщений: 1) пересылка байта данных от устройства ввода; 2) пересылка байта данных к устройству вывода; 3) считывание байта данных из памяти или запись в память; 4) генерирование в шину данных специального байта, называемого управляющим словом и предназначенного для установления правильного схемного соединения.

Работа МП (или центрального процессорного элемента ЦПЭ) по реализации каждой команды программы пользователя основана на принципе микропрограммного управления. Это означает, что каждая команда реализуется как некоторая последовательность микрокоманд или микроопераций, приводящая к требуемому результату. Считываемая из памяти микропроцессором команда, вернее, ее 8-разрядный двоичный код (код операции), поступает в регистр команд, где и хранится в течение времени выполнения команды. По результату дешифрирования кода команды происходит формирование последовательности микрокоманд (микропрограммы), процесс выполнения которой и определяет все последующие операции, необходимые для выполнения считанной команды.

Таким образом, выполнение каждой считанной ЦПЭ команды программы пользователя осуществляется в строго определенной последовательности, задаваемой кодом команды. При этом выполнение отдельных микроопераций синхронизируется во времени сигналами Ф1 и Ф2 тактового генератора. Одним из важнейших понятий всего процесса выполнения команд программы является понятие машинного цикла.

В микропроцессоре КР580ИК80А процесс выполнения каждой команды можно разбить на ряд основных операций. Время, отведенное на выполнение операции обращения к памяти или к устройству вывода, составляет машинный цикл.

Таким образом, процесс выполнения команды состоит из стольких машинных циклов, сколько обращений к памяти или к устройствам ввода/вывода требуется для ее исполнения. Машинный цикл в свою очередь состоит из нескольких машинных тактов.

Каждая команда в зависимости от ее вида может занимать от одного до пяти машинных циклов. Микропроцессор КР580ИК80А имеет 10 типов машинных циклов, перечисленных в табл. 6.2, а каждый машинный цикл может состоять из 3 — 5 машинных тактов. Под машинным тактом подразумевается интервал времени, соответствующий одному периоду тактовых импульсов, подаваемых от синхрогенератора.

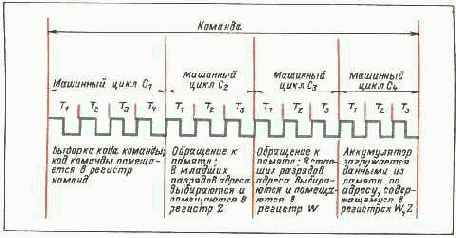

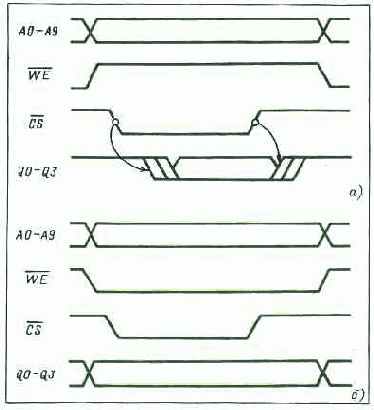

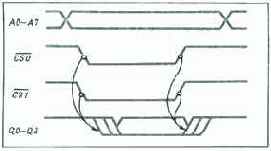

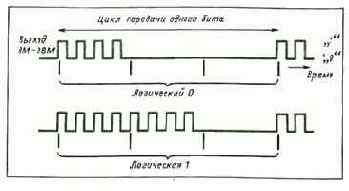

Рис. 4.5. Временная диаграмма для команды, требующей четыре машинных цикла

Для организации машинных циклов требуется формирование строго синхронизированной во времени последовательности управляющих сигналов, обеспечивающих правильные пути прохождения данных в строго определенные моменты времени, и выполнение требуемых микроопераций. Как уже отмечалось, исходными данными для этого являются результаты дешифрирования операционного кода команды. Выполнение команды всегда начинается с цикла обращения к памяти, в результате которого производится считывание кода, интерпретируемого МП как код операции. Будем обозначать машинные циклы одной команды символами Cl, C2 и т. д., а машинные такты одного цикла — символами Tl, T2 и т. д. Таким образом, машинный цикл С1 — это всегда цикл выборки команды. Его длительность обычно — четыре или пять тактов. Последующие циклы С2 — С5 состоят обычно из трех тактов. Для простых операций, таких как арифметические, команды занимают четыре или пять тактов. Команды более сложных операций требуют для выполнения до 18 машинных тактов.

В качестве примера рассмотрим команду LDA (ЗАГРУЗИТЬ данные в аккумулятор), требующую для реализации четыре машинных цикла. На рис. 4.5 приведена временная диаграмма команды LDA. Эта команда переписывает в аккумулятор данные, содержащиеся в определенной ячейке памяти.