ОСНОВНЫЕ СВЯЗИ И СТРУКТУРА ШИН

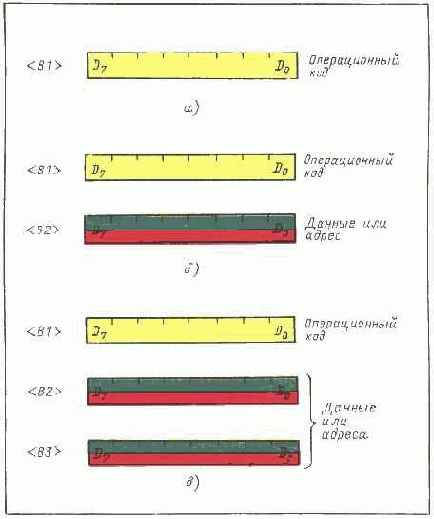

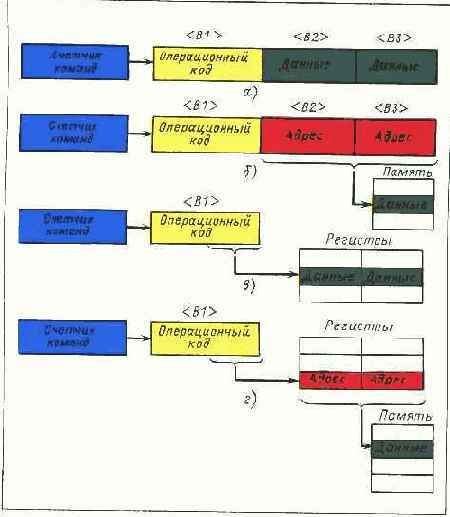

В микро-ЭВМ, построенных на базе микропроцессоров, все связи между отдельными функциональными блоками осуществляются, как правило, так называемыми шинами. Под шиной подразумевается физическая группа линий передачи сигналов, обладающих функциональной общностью (по каждой линии передается один двоичный разряд информации). Так, например, данные в машине обычно передаются к различным ее функциональным узлам параллельно по восьми линиям. Физически шины реализуются в виде параллельных проводящих полосок печатной платы или в виде связанных в жгут проводов. Соответствующая группа из восьми линий передачи данных называется 8-разрядной шиной данных. Кроме шины данных в микро-ЭВМ выделяют шину передачи адресов, или шину адреса, и шину управления. Микро-ЭВМ с такой организацией связей относят к системам, обладающим архитектурой с тремя шинами.

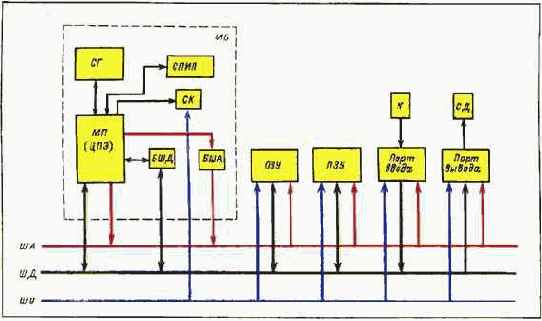

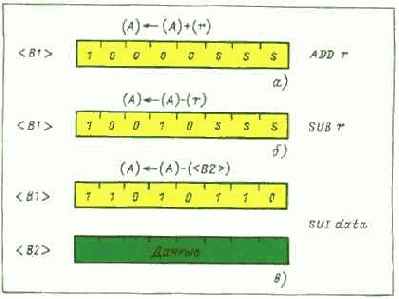

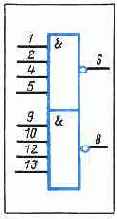

Рис. 4.2. Упрощенная архитектура ЭВМ с тремя шинами

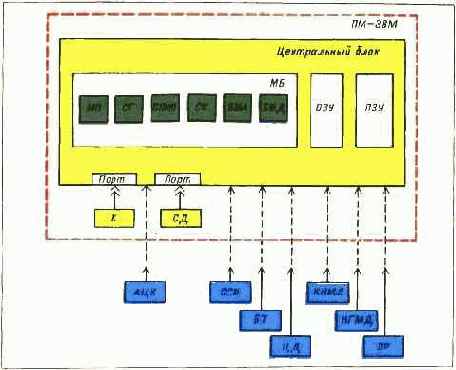

Типовые связи в архитектуре ЭВМ с тремя шинами в общем случае будут иметь вид, представленный на рис. 4.2, если в качестве основных функциональных блоков машины использовать микропроцессорный блок (МБ), ОЗУ, ПЗУ и порты ввода/вывода. Линии шин адреса (ША) и управления (ШУ) являются однонаправленными [Здесь не рассматривается режим прямого доступа к памяти]. В них сигналы протекают в одном направлении — от центрального процессорного элемента ко всем остальным блокам. Шина адреса является 16-разрядной. Число линий шины управления определяется составом сигналов, формируемых системным контроллером.

Передаваемые по ША сигналы формируются в МП. Они необходимы для определения пути передачи внутри микро-ЭВМ, в том числе для выбора ячейки памяти, куда необходимо занести или откуда необходимо считать информацию. В определении тракта передачи данных могут принимать участие и управляющие сигналы, подсоединяющие или, напротив, блокирующие те или иные устройства микро-ЭВМ.

В отличие от ША и ШУ шина данных (ШД) является шиной двунаправленной.

Данные по линиям шины могут передаваться от микропроцессора к какому-нибудь устройству микро-ЭВМ либо пересылаться в МП от какого-то устройства, доступ к которому обеспечивают сигналы адресной шины.

Естественно, что в каждый момент времени данные могут передаваться лишь в одном направлении, определяемом режимом работы микропроцессора. К основным режимам работы МП можно отнести: запись данных в память машины; чтение данных из памяти машины; пересылку данных в устройство ввода/вывода; чтение данных с устройства ввода/вывода; выполнение операций с содержимым внутренних регистров микропроцессора.

При реализации последнего режима внешние по отношению к МП шины микро-ЭВМ не используются, т. е. все действия происходят внутри МП. Реализация первых четырех режимов оказывает определяющее влияние на работу шины данных.

Работа по реализации программы любой микро-ЭВМ, построенной по типу архитектуры с тремя шинами, состоит в выполнении следующих действий для каждой команды программы.

1. Микропроцессор формирует адрес, по которому хранится код операции команды, переводя в соответствующее состояние шину адреса.

2. Код операции считывается из памяти по сформированному адресу и пересылается в микропроцессор.

3. Команда дешифрируется (идентифицируется) микропроцессором.

4. Микропроцессор "настраивается" на выполнение одного из перечисленных выше пяти основных режимов в соответствии с результатами дешифрирования считанного из памяти кода команды.

Перечисленные выше пять режимов являются основными, но не единственно возможными. Существуют и другие, рассматриваемые в гл. 6.

Перейдем теперь к окончательному оформлению функциональной схемы ПМ-ЭВМ.

ПОДГОТОВКА ПМ-ЭВМ К РАБОТЕ

После того как проведенные проверки подтвердили работоспособность микро-ЭВМ, можно приступить к ее эксплуатации. От условий эксплуатации зависит окончательное конструктивное оформление ПМ-ЭВМ. В лабораторных условиях можно оставить все в таком виде, в каком производилась отладка, т. е. соединенные проводами или плоскими кабелями отдельные платы, клавиатуру и лабораторные источники питания, приведя только в порядок проводку и проверив все соединения.

Если предполагается эксплуатировать ПМ-ЭВМ в стационарных условиях класса или аудитории, то желательно конструктивно оформить ее в виде отдельного стенда, на котором должны быть жестко закреплены все узлы и устройства с аккуратно выполненными связями между ними с помощью кабелей наименьшей возможной длины. При этом можно пользоваться либо лабораторными источниками питания, либо встроенными в стенд автономными. ПМ-ЭВМ потребляет (без дополнительных периферийных устройств) от источника + 5 В примерно 1,3 А, от источника + 12 В примерно 30 мА и от источника -5 В примерно 30 мкА. Желательно иметь некоторый, например двукратный, запас по источникам питания, имея в виду подключение дополнительной памяти, периферийных микросхем и устройств. В переносном варианте ПМ-ЭВМ легко размещается вместе с источниками питания в небольшом чемоданчике размерами ЗбОх 250х 80 мм и массой не более 3 кг.

После включения ПМ-ЭВМ переведите переключатель К18 в положение АВТОМАТ и нажмите кнопку СБРОС. После отпускания кнопки СБРОС на индикаторах портов 001 и 000 высветится адрес начальной ячейки ОЗУ (014Q OOOQ), а на индикаторах порта 002 — содержимое этой ячейки. Нажимая кнопку И, убедитесь, что адрес, индицируемый портами 001 и 000, при каждом нажатии увеличивается на единицу. Снова нажмите кнопку СБРОС и убедитесь, что цифровые клавиши функционируют нормально, т. е. при каждом нажатии индицируемое портом 002 число сдвигается на три двоичных разряда влево и освободившееся место заполняется числом, соответствующим нажатой клавише.

Убедитесь также, что при нажатии кнопок СБ или МБ информация, индицируемая портом 002, перемещается в порты 001 или 000 соответственно. Снова нажмите и отпустите кнопку СБРОС и переведите переключатель К18 в положение ШАГ. Порт 002 индицирует состояние шины данных, соответствующее исполнению машинного цикла одной из команд программы-монитора от адреса OOOQ 220Q до OOOQ 251Q. При нажатии кнопки К17 МАШИННЫЙ ЦИКЛ последовательно исполняются команды между данными адресами. Этот процесс повторяется неограниченно долго — до тех пор, пока не будет нажата какая-либо из кнопок клавиатуры от К1 до К16, и тогда произойдет переход к подпрограмме временной задержки. Снова нажмите и отпустите кнопку СБРОС. Порт 002 индицирует код 303Q. Это код команды JMP М1, команды программы-монитора, находящейся по адресу OOOQ OOOQ. Последовательно нажимая кнопку К17 МАШИННЫЙ ЦИКЛ, можно проследить исполнение программы-монитора по машинным циклам. Просмотреть по шагам исполнение рабочей программы можно только в том случае, если она циклическая. Тогда переключатель К18 первоначально должен находиться в положении АВТОМАТ. Нажимаем и отпускаем кнопку СБРОС, вводим начальный адрес рабочей программы в соответствии с инструкцией (§ 7.4), нажимаем кнопку П и переключаем К18 в положение ШАГ. Порт 002 индицирует состояние шины данных, соответствующее исполнению машинного цикла одной из команд рабочей программы. При нажатии кнопки К17 последовательно исполняются команды рабочей программы. Правильность их исполнения проверяется по индикаторам порта 002. Не забывайте перед началом работы перевести переключатель К18 в положение АВТОМАТ и нажать кнопку СБРОС.

Появление микропроцессоров сыграло важную роль

Появление микропроцессоров сыграло важную роль в развитии вычислительной техники, средств обработки информации и управляющих устройств, являющихся основой автоматизации в различных сферах человеческой деятельности. Неослабевающий интерес к микропроцессорам объясняется такими их особенностями, как низкая стоимость, высокая надежность, компактность и значительные функциональные и вычислительные возможности, позволяющие применять их даже там, где использование средств цифровой обработки информации ранее считалось нецелесообразным. В настоящее время как у нас в стране, так и за рубежом издается весьма обширная литература по микропроцессорной технике и возможностям ее применения. И все же книг с описанием реально построенных конструкций и устройств на базе микропроцессоров явно недостаточно для удовлетворения постоянно растущего спроса на такие публикации. Именно это побудило авторов взять на себя смелость написать нечто вроде руководства, ориентированного на читателя, пожелавшего ознакомиться с работой простейшей микро-ЭВМ или заняться ее изготовлением.

Конечно, эта книга — не инструкция по изготовлению микро-ЭВМ в полном смысле этого слова, хотя в ней довольно подробно описываются конструкция вычислительной машины и ее работа. Основная цель книги — помочь разобраться в том, что такое микропроцессор, как он работает, как необходимо его программировать и как на его основе можно создавать разнообразные устройства, применяющиеся в технике, в быту, в повседневной практической деятельности.

Современный микропроцессор - довольно сложное устройство, работу которого не удается описать в деталях вне связи с системой, в составе которой он функционирует (в отличие от других более простых электронных приборов, таких например, как электронная лампа). К сожалению, в специальной литературе микропроцессор в подавляющем большинстве случаев описывается автономно. Из такого описания не всегда понятны детали его работы и особенности применения.

Предлагаемая читателям книга в некоторой степени восполняет этот пробел. Авторами описывается схема простейшей микро-ЭВМ как пример простейшей микропроцессорной системы. Будет или не будет читатель строить эту микро-ЭВМ — не так уж и важно. Важно, что на базе этой конкретной микропроцессорной системы он получит необходимые сведения о работе микропроцессора и сможет построить в дальнейшем аналогичные системы по своему выбору и вкусу.

Выступая в 1970 г. с докладом о перспективах развития и применения вычислительной техники на конференции в Московском физико-техническом институте, академик В. М. Глуш-ков говорил о том, что недалек тот день, когда вычислительная техника шагнет в повседневную жизнь и буквально каждая семья сможет получить доступ к вычислительным ресурсам. Во времена господства универсальных вычислительных машин-гигантов это высказывание представлялось по меньшей мере весьма смелым прогнозом. Но прошли годы и вот уже микроэлектроника стучится в двери наших квартир, появляется на рабочих местах в учреждениях, приближая тот день, когда вычислительные машины станут для нас столь же привычными в быту, как холодильники, стиральные машины и цветные телевизоры.

Отсюда ясно, как важна популяризация тех знаний, которые раньше были необходимы лишь специалистам. В особенности это касается знаний в следующих трех областях: математической логике, программировании и электронике. Но даже специалисты, равным образом ориентирующиеся в указанных трех областях, в настоящее время встречаются не так уж часто. Пользователи ЭВМ прошлых поколений практически никогда не сталкивались с аппаратной реализацией своих программ, а специалисты в области электроники, как правило, не занимались программированием. Поэтому широкая подготовка специалистов нового типа — насущная проблема сегодняшнего дня.

Данная книга вовсе не претендует на роль учебного пособия с изложением основ математической логики, электроники и программирования. Цель у книги другая — привлечь широкий круг читателей к относительно новому, увлекательному миру конструирования микроэлектронных устройств на базе микропроцессорной техники, сфера применения которых не ограничивается традиционными вычислительными задачами.

Создание программируемых устройств с широкими функциональными возможностями - микроэлектронных помощников ( пусть на первое время совсем простых), повышающих эффективность интеллектуальной деятельности на производстве и дома, - вот, может быть, самая интересная и многообещающая область исследований в наш век всеобщей компьютеризации.

Необходимо заметить, что авторы вовсе не хотели бы склонить будущих конструкторов к попытке воспроизвести копию промышленной микро-ЭВМ. Любительским конструкциям трудно тягаться с изделием, выпускаемым промышленностью. Тем не менее широкое привлечение любителей к микроэлектронному конструированию позволит в ряде случаев найти те оригинальные технические решения, которые в дальнейшем могут быть использованы целиком в конструкциях соответствующих промышленных изделий или положены в их основу. Для чтения книги не требуется специальных знании в области микропроцессорной техники. Тем не менее предполагается, что читатель сможет, пользуясь приведенными в книге рекомендациями самостоятельно собрать простую ЭВМ из малодефицитных деталей, отладить ее, проделать на ней ряд упражнении по программированию решения различных задач, а также изучить способы подсоединения дополнительных внешних устройств, значительно расширяющих возможности построенной машины. Хотя описываемая микро-ЭВМ построена по универсальной схеме, допускающей наращивание аппаратуры до широких пределов (скажем, до масштабов персональной ЭВМ), основное назначение ее - учебное, т. е. позволяющее в максимально короткое время получить навыки основ программирования и проектирования микропроцессорных систем. С этой целью читателю дается весь необходимый материал, приводятся реальные схемы с реальными характеристиками. В отличие от большинства подобных изданий в книге описываются не только отдельные узлы машины, но и целиком вся ее схема. Выводы всех микросхем промаркированы, и каждая микросхема описана в деталях. Поэтому читателю нет необходимости обращаться к зачастую труднодоступным справочным источникам.

Главы 1-4, а также приложение 1 (система команд микро-процессора КР580ВМ80А) написаны В.Н. Захаровым, гл. 5- 7 написаны А. Л. Дудко, а гл. 8-10 - Л. Н. Буреевым. Принципиальная электрическая схема описываемой микро-ЭВМ (приложение 2) разработана А. Л. Дудко, а описываемые схемы сопряжения микро-ЭВМ с дополнительными внешними устройствами (в том числе с бытовыми телевизором и магнитофоном) , а также схема статического аппаратного эмулятора разработаны Л. Н- Буреевым. Предисловие к книге написано авторами совместно.

Авторы позволяют себе надеяться, что книга окажется полезной не только будущим конструкторам микро-ЭВМ, но и всем тем, кто стремится расширить свои знания в области применения микропроцессорной техники.

Авторы выражают признательность рецензенту канд. техн. наук В. Ф. Корнюшко и редактору проф. Д. А. Поспелову за доброжелательную критику и замечания, которые способствовали улучшению содержания и стиля книги.

Все замечания по содержанию книги, методике изложения, а также все предложения по усовершенствованию схемы и конструкции описываемой машины авторы примут с благодарностью. Пожелания и замечания просьба направлять по адресу: 113114, Москва, М-114, Шлюзовая наб., 10, Энергоатомиздат.

Авторы

ПРОГРАММА-МОНИТОР

Программа-монитор (или просто монитор) — это программа, которая управляет работой микро-ЭВМ. Монитор выполняет следующие функции: подготовку к работе устройств микро-ЭВМ после включения питания и повторных перезапусков, обслуживание индикаторов и клавиатуры, выполнение указаний пользователя по реализации программы. Микро-ЭВМ выполняет программу-монитор все то время, когда она не выполняет какую-либо программу пользователя.

Ниже приведен полный текст программы-монитор. При первом прочтении можно пропустить дальнейший текст данного параграфа, но при отладке ПМ-ЭВМ и работе с нею необходимо четкое понимание функционирования монитора, для чего и приводится ее детальное описание.

Текст программы состоит из трех столбцов. Первый столбец содержит адреса ячеек памяти, второй столбец - содержимое этих ячеек в восьмеричном коде, а третий столбец — ассемблерную запись программы.

После подачи всех необходимых напряжений на микросхемы и микропроцессор микро-ЭВМ начинает работать. При этом содержимое всех регистров микропроцессора и ячеек ОЗУ устанавливается случайным образом. Поэтому в микро-ЭВМ происходит в этот момент неуправляемый и непредсказуемый процесс. Для того чтобы остановить его и пустить по вполне определенному руслу, в микропроцессоре КР580ИК80А имеется вход RESET (вывод 72). На этот вход подается высокий уровень, который вырабатывается при помощи специальной схемы сразу после включения питания (см. гл. 6) или при нажатии на кнопку СБРОС. По этому сигналу микропроцессор заносит в счетчик команд (PC) во все разряды нули. Это означает, что следующая команда будет считываться из ячеек с нулевым адресом. По этому адресу размещается первая команда монитора. Для того чтобы монитор уже находился в памяти микро-ЭВМ после ее включения, он помещается в ПЗУ. Кроме того что монитор занимает память ПЗУ, он, как и всякая программа, при своей работе использует ячейки ОЗУ и регистры микропроцессора. Какие ячейки ОЗУ и как он использует, будет ясно после разбора самой программы.

Итак, первая команда монитора, расположенная по адресу 000000Q, - команда безусловного перехода JMP Ml, которая передает управление команде, расположенной по адресу 000070Q. Команда JMP Ml занимает три байта. Байты с 000 003 Q по 000 067 Q не используются. Эту область ПЗУ следует оставить незапрограммированной, так как она может понадобиться для расширения возможностей микро-ЭВМ по работе с прерываниями. Под меткой Ml (по адресу 000070Q) находится команда LXI SP, 010000Q. Эта команда загружает константу 010000Q в указатель стека (SP), чтобы он указывал на первую несуществующую ячейку ОЗУ. Тогда при первом занесении данных в стек (ячейки которого располагаются в ОЗУ) SP будет увеличен на единицу и будет указывать последнюю ячейку физически существующего ОЗУ, куда и поместятся данные. При дальнейших обращениях стек будет "расти" от старших адресов памяти к младшим при записи в него и "уменьшаться" при считывании. Если пользователь далее будет правильно использовать команды записи и считывания (их число должно быть одинаковым), никогда не произойдет ошибки обращения к стеку. Обратим здесь внимание на то, что восьмеричная константа, записанная в ассемблерной строке под меткой Ml, приобрела другую кодировку при записи в память в ячейки 000071Q и 000 072 Q. Чтобы понять, что произошло при переходе от записи на ассемблере к реальному расположению константы в памяти, запишем сначала эту константу в двоичном коде: 010000Q равняется 0001000000000000В. Если теперь разбить это 16-разрядное двоичное число на два байта, то получится 00010000В и 00000000В, или в восьмеричной системе 020Q и OOOQ. Эти числа и записаны в ячейки с адресами 000 072 Q и 000071Q соответственно. Этот перевод константы от той формы, в которой она записана на ассемблере, к реальному расположению в памяти будет встречаться еще во многих командах монитора.

Следующая команда LXI Н, 006 000 Q загружает пару регистров H-L константой 006 000Q.

Эта константа является адресом первой ячейки ОЗУ. Загрузка SP и H-L начальными значениями выполняется только один раз при входе в монитор (после сигнала RESET). В дальнейшем эта пара регистров будет использоваться для хранения адреса ячейки памяти, с которой в данный момент работает программист.

Итак, SP установлен таким образом, что поле стека будет находиться в старших адресах ОЗУ, а в H-L находится адрес первой ячейки ОЗУ. Следующие семь команд, занимающие ячейки с 000076Q по 000110Q, служат для того, чтобы высветить на индикаторах адрес ячейки памяти, с которой в настоящее время работает программист, и ее содержимое. Команда М2: MOV С, М (адрес 000 076 Q) переписывает данные из ячейки, адрес которой хранится в H-L (при первом проходе данного места программы это адрес первой ячейки ОЗУ), в регистр С. Далее команда MOV A, H переписывает данные из регистра Н в аккумулятор, чтобы с помощью следующей команды OUT 001Q вывести ее на индикаторы с адресом 001Q. Данные переписываются в аккумулятор перед их выводом этой командой (в двух последующих аналогичных случаях применяется команда OUT OOOQ и OUT 002Q), потому что команда OUT может переслать в устройство вывода только содержимое аккумулятора. После выполнения команды OUT 001 Q на соответствующих индикаторах высветится содержимое регистра Н. Каждый светодиод, которому соответствует единица в каком-либо разряде регистра Н, загорится, а каждый светодиод, которому соответствует нуль в каком-либо разря-пе Н погаснет. Аналогично на светодиодах порта OOOQ высветится содержимое регистра L (команды MOV A, L и OUT OOOQ) и порта 002 Q - регистра С (команды МЗ: MOV А, С и OU 1 00?Q) После этого выполняется команда М4: CALL SKL, которая вызывает подпрограмму SKL, обслуживающую клавиатуру. Прежде чем переходить к описанию этой подпрограммы, опишем еще одну подпрограмму DL, которая вызывается из подпро-граммы SKL.

Подпрограмма DL служит для задержки выполнения программы на 10 мс.

Такие задержки часто необходимы при работе с внешними устройствами, быстродействие которых значительно меньше, чем у микро-ЭВМ. Поэтому эта подпрограмма, находящаяся и используемая в мониторе, написана таким образом что сохраняет значение всех регистров и ячеек памяти во время своей работы. Она может быть вызвана из других программ пользователя. Подпрограмма DL начинается с ячейки 000 277 Q Команды PUSH PSW и PUSH D переписывают в стек содержимое аккумулятора, регистра состояний и пары регистров D-E для того, чтобы освободить эти регистры и использовать далее для своей работы, а перед выходом из подпрограммы восстановить их старое содержание. Затем пара регистров D-E загружается с помощью команды LXI D, 001 016Q константой 001016Q. Следующие пять команд образуют цикл. Команда N:DCX D уменьшает содержимое пары регистров D-E, вычитая из хранящегося в них двоичного числа единицу. Затем старший байт пары D-E командой MOV A, D переписывается в аккумулятор Далее команда ORA E выполняет поразрядно логическую операцию ИЛИ над содержимым аккумулятора и регистра Е и результат этой операции записывается в аккумулятор, при этом если содержимое А и Е (или D и Е) не равно нулю, сбрасывается флаг признака нуля результата Z. Это приводит к тому что следующая команда JNZ N (адрес 000 307 Q) осуществляет переход к метке N (адрес 000304Q) и фрагмент программы от метки N до команды JNZ N (или, что то же самое, от адреса 000304Q до 000311Q) будет повторяться до тех пор пока в обоих регистрах D и Е не образуются нули. Следовательно этот фрагмент программы выполняется 001016Q раз. Обозначим буквой N с соответствующим индексом число машинных тактов определенной команды. Тогда число тактов при однократном выполнении этого фрагмента N0 =Ndcxd + + Nmova,d+Norae+Njnzn = 5 + 5 + 4+10= 19.

Так как длительность одного такта при использовании кварцевого резонатора на частоту 9 МГц равняется 1 мкс (см. гл. 6), время выполнения этого фрагмента 19 мкс, а чтобы выполнить его 001 016Q раз, нужно 9994 мкс.

Следовательно, выполнение этой программы задерживает выполнение программы, вызвавшей ее, примерно на 10 мс. После того как выполнено 001 016 Q циклов и содержимое D и Е равно нулю, флаг Z не устанавливается командой ОКА Е и командой JNZ N не передает управление к метке N. Тогда выполняются команды POP D и POP PSW, которые восстанавливают содержимое пары регистров D-E, аккумулятора и слова состояний. Затем команда RET передает управление команде, следующей за той командой CALL DL, которая вызвала эту подпрограмму.

Рассмотрим теперь подпрограмму SKL. Эта подпрограмма обеспечивает работу клавиатуры микро-ЭВМ. Она располагается в области ПЗУ с адресами 000 177Q - 000 276Q. При ее вызове командой CALL SKL управление передается команде, располагаемой по адресу 000177Q. Команда SKL: MVI А, 000Q загружает в аккумулятор OOOQ, а следующая команда OUT 003Q записывает содержимое младших четырех битов аккумулятора, т. е. 0000В, в четыре триггера микросхем К155ТМ7 (см. микросхему D22 на рис. 7.7). Следовательно, на выходах триггеров этой микросхемы (выводы 16, 15, 10, 9) устанавливаются нули. При этом если нажать хотя бы одну из кнопок К1 — К16, то на соответствующем входе микросхемы К589АП16 (D23) установится также нуль. Далее следующая команда М5: IN 003Q переписывает в четыре младших бита аккумулятора те логические состояния, которые в момент выполнения этой команды присутствуют на входах микросхемы D23. Затем команда ANI 017Q путем выполнения логической операции И записывает в старшие четыре разряда аккумулятора нули, а младшие четыре разряда оставляет такими, какие они были. После этого команда CPI 017Q сравнивает содержимое аккумулятора с константой 017Q (00001111В). В результате этого сравнения в регистре состояний процессора будет установлен флаг нулевого результата, если при выполнении команды М5: IN 003Q на входах микросхемы D23 (выводы 4, 7, 9, 12) были единицы, т. е. ни одна кнопка К1-К16 не была нажата. Если хотя бы одна из кнопок была нажата, то флаг нулевого результата после сравнения с 017 Q не будет установлен и следующая команда условного перехода JNZ М5 вызовет переход к метке М5.

Таким образом, фрагмент программы, начиная с метки М5 и кончая командой JNZ M5, будет выполняться до тех пор, пока все кнопки не будут отпущены. Этот фрагмент программы нужен потому, что после нажатия кнопки монитор выполняет все необходимые операции столь быстро, что пользователь еще не успевает отпустить кнопку, а программа уже готова обработать следующее нажатие кнопки. Поэтому если бы не было этого фрагмента, одно нажатие кнопки воспринималось бы как несколько нажатий, что приводило бы к неправильной работе монитора.

Прежде чем рассматривать дальше работу подпрограммы, обратим внимание на тот факт, что при нажатии кнопок К1-К16 происходит дребезг контактов, рассмотренный в гл. 6. Там же приводилась специальная схема, позволяющая устранить это явление. Дребезг контактов (см. рис. 6.14) приводит к тому, что на входе D23 вместо идеального перехода из нуля в единицу при размыкании контактов кнопки и из единицы в нуль при замыкании контактов кнопки имеется серия переходов. Каждый такой переход может быть воспринят как новое нажатие на кнопку, поэтому необходимо принять специальные меры, чтобы этого не произошло. Можно было бы снабдить каждую кнопку электронной схемой для подавления дребезга контактов (см. рис. 6.13), но можно воспользоваться программным методом, описываемым ниже. В подпрограмме для этого после команды JNZ M5 идет команда CALL DL, которая вызывает подпрограмму временной задержки. Выполнение программы задерживается на 10 мс. За это время дребезг контактов заканчивается.

Следующий фрагмент программы "ожидает" нажатия кнопки и вводит код нажатой кнопки в аккумулятор. В качестве рабочих регистров будут использоваться пара D-E и аккумулятор, поэтому командой PUSH D содержимое пары регистров D-E сохраняется в стеке. Следующие две команды М8: MVI D, 003Q и MVI Е, 376Q загружают в регистры D и Е коды 003 Q и 376Q соответственно. Затем команда М7: MOV A, E переписывает содержимое регистра Е в аккумулятор, а команда OUT 003Q переписывает четыре младших разряда аккумулятора в триггеры микросхемы D22.

После этого команда RLC сдвигает содержимое аккумулятора на один бит влево, а команда MOV Е, А переписывает его в регистр Е. Содержимое регистров и состояние выходов триггеров микросхемы D22 в двоичном коде в этот момент представлено в первой строке табл. 7.5.

Та б л и ц а 7.5

|

Номер строки, номер проход. |

Содержимое регистров |

Состояние выходов триггеров D22 |

||||||

|

|

D |

Е |

9 |

10 |

15 |

16 |

||

|

1 |

00 000 01 1 |

11 |

111 |

101 |

1 |

1 |

1 |

0 |

|

2 |

00 000 010 |

11 |

111 |

011 |

1 |

1 |

0 |

1 |

|

3 |

00 000 001 |

11 |

110 |

111 |

1 |

0 |

1 |

1 |

|

4 |

00 000 000 |

11 |

101 |

111 |

0 |

1 |

1 |

1 |

Во время четвертого прохода содержимое регистра станет равным 377Q и команда JNZ M7 (адрес 000 246Q) не осуществит переход к М7, а будет выполняться следующая за ней -команда безусловного перехода JMP M8, в результате чего команды М8: MVI D, 003Q и MVI E, 376Q загрузят регистры D и Е и фрагмент от М7: MOV A, E до JNZ M7 повторится опять 4 раза.

Этот процесс будет повторяться до тех пор, пока не нажата ни одна кнопка и на входах 4, 7, 9, 12 микросхемы D23 находятся высокие уровни, а следовательно, в аккумуляторе после выполнения команды ANI 017Q (адрес 000 233 Q) находится код 017Q. Если какая-либо кнопка нажата, то код в аккумуляторе не равен 017Q и команда JNZ Мб осуществляет переход к команде Мб: CALL DL, которая вызывает подпрограмму временной задержки для того, чтобы переждать дребезг контактов после нажатия кнопки. Значения кода в аккумуляторе после выполнения команды ANI 017Q в зависимости от кода на выходах триггеров микросхемы D22 и от того, какая нажата кнопка, приведены в табл. 7.6.

Таблица 7.6

|

|

Выход |

|

Вход мик- |

|

|

Номер строки |

триггера микро- Код в ре-схемы гистре D В22,на |

Нажатая кнопка |

росхемы D23, на котором низкий |

Код в аккумуляторе |

|

|

котором |

|

уровень |

|

|

|

низкий |

|

|

|

|

|

уровень |

|

|

|

|

1 |

9 00 000 000 |

К1 |

4 |

00001 ПО |

|

|

|

К5 |

7 |

00001 101 |

|

|

|

К9 |

9 |

00001 011 |

|

|

|

К13 |

12 |

00000 111 |

|

2 |

10 00000001 |

К2 |

4 |

00001 ПО |

|

|

|

Кб |

7 |

00 001 101 |

|

|

|

К10 |

9 |

00001 011 |

|

|

|

К14 |

12 |

00 000 1 1 1 |

|

3 |

15 00000010 |

КЗ |

4 |

00001 110 |

|

|

|

К7 |

7 |

00 001 101 |

|

|

|

К11 |

9 |

00001 011 |

|

|

|

К15 |

12 |

00 000 1 1 1 |

|

4 |

16 00000011 |

К4 |

4 |

00001 110 |

|

|

|

К8 |

7 |

00 001 101 |

|

|

|

К12 |

9 |

00001 011 |

|

|

|

К16 |

12 |

00000 111 |

Тогда следующая команда PUSH PSW сохраняет содержимое аккумулятора и слово состояний микропроцессора в стеке для того, чтобы можно было дальше использовать аккумулятор. Команда MOV A, D переписывает содержимое регистра D в аккумулятор, а команда ADI 004Q прибавляет к содержимому аккумулятора константу 004Q. После этого команда MOV D, А переписывает результат сложения в регистр D, а команда POP PSW восстанавливает содержимое аккумулятора и слово состояний микропроцессора, считывая их из стека. Далее команда безусловного перехода JMP M1C осуществляет переход к команде М10: RRC, т. е. повторяет фрагмент программы, начиная с М10. Теперь ясно, что в зависимости от кода в аккумуляторе (табл. 7.6) фрагмент программы от команды JNC M9 (адрес 000 260Q) до командь: JMP M10 (адрес 000 271Q) будет выполняться нуль раз для первой строки таблицы, 1 раз — для второй. 2 раза — для третьей и 3 раза — для четвертой. Это значит, что к коду в регистре (см, табл. 7.6} соответствующее число раз прибавится константа 004Q. Следовательно, в регистре D после выполнения команды JNC M9 будет содержаться код, зависящий от нажатой кнопки. Все возможные коды перечислены в табл. 7.7

Таблица 7.7

|

Нажатая кнопка |

Код в регистре D в двоичной системе |

Код в регистре D в восьмеричной системе |

Мнемоническое название кнопки |

|

К1 |

00 000 000 |

000 |

0 |

|

К2 |

00 000 001 |

001 |

i |

|

КЗ |

00000010 |

002 |

2 |

|

К4 |

00000011 |

003 |

3 |

|

К5 |

00000 100 |

004 |

4 |

|

Кб |

00 000 101 |

005 |

5 |

|

К7 |

00 000 110 |

006 |

6 |

|

К8 |

00 000 111 |

007 |

7 |

|

К9 |

00 001 000 |

010 |

СБ |

|

К10 |

00 001 001 |

011 |

МБ |

|

К11 |

00001 010 |

012 |

К |

|

К 12 |

00001 011 |

013 |

П |

|

К13 |

00 001 100 |

014 |

- |

|

К14 |

00001 101 |

015 |

= |

|

К15 |

00001 110 |

016 |

= |

|

К16 |

00 001 111 |

ОП |

= |

Затем командой POP Г восстанавливается то содержание регистра D, которое было до начала работы подпрограммы SKL. На этом работа подпрограммы заканчивается и команда RET загружает в счетчик команд адрес команды, следующей за той, которая вызвала переход к подпрограмме. Заметим, что подпрограммы SKL и DL не портят при своей работе содержимое каких-либо регистров. Результат своей работы — код, соответствующий нажатой кнопке, — подпрограмма SKL возвращает в аккумулятор. Итак, была нажата кнопка, подпрограмма SKL выработала код, соответствующий этой кнопке, и поместила его в аккумулятор. Работа монитора продолжается с команды CPI 010Q (адрес 000113Q). Эта команда сравнивает содержимое аккумулятора с константой 010Q. Это сравнение происходит путем вычитания из кода, хранящегося в аккумуляторе, кода 010Q (по правилам двоичного вычитания), хотя содержимое аккумулятора не портится. При этом если значение двоичного числа, которое выражено кодом, содержащимся в аккумуляторе, меньше 010Q (или 8D), то по правилам двоичного вычитания происходит заем и устанавливается флаг переноса С, если больше или равно 010Q - то флаг не устанавливается. Затем команда JNCM11 осуществляет переход к метке МП (адрес 000134Q), если код нажатой кнопки больше или равен 010Q, если нет, то выполняются команды, следующие за JNC МП. Коды, меньшие 010Q, соответствуют кнопкам К1-К8 и обрабатываются МОНИТОРОМ ПО-ОСОбому, потому что эти кнопки кодируют восьмеричные цифры от 0 до 7 (см. табл. 7.7) для ввода в микро-ЭВМ. Остальным кнопкам присвоены специальные функции, которые выполняются монитором (см. ниже).

Рассмотрим, как происходит ввод восьмеричного числа в микро-ЭВМ. Напомним, что регистр С используется для временного хранения введенного числа до того момента, как онс будет переписано в память по адресу, хранящемуся в паре регистров H-L. После того как была нажата одна из кнопок К1-К8, программа переходит к команде MOV В, А (адрес 000 120Q), которая переписывает код нажатой кнопки из аккумулятора в регистр В.

Затем код, содержащийся в регистре С ( этот код был высвечен на индикаторах порта OOOQ), переписывается в аккумулятор командой MOV А, С и сдвигается тремя командами RAL на три бита влево. После этого с помощью команды ANI 3 70Q очищаются три младших бита, а с помощью команды ORA В на эти места записываются новые трк разряда кода нажатой кнопки. В результате в аккумуляторе готов новый код для индикации на индикаторах порта OOOQ, Далее содержимое аккумулятора переписывается в регистр С командой MOV С5 А, а затем команда JMP M3 осуществляет переход к фрагменту программы, реализующему индикацию.

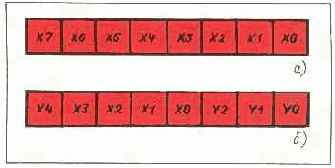

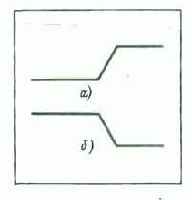

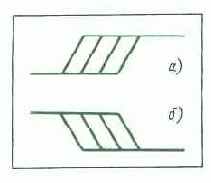

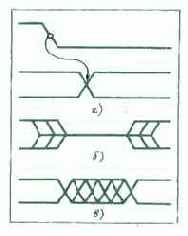

На индикаторе порта OOOQ пользователь видит следующее. Если до нажатия кнопки состояния индикаторов были ХО — Х7 (рис. 7.10,д), то после нажатия эти состояния сдвигаются на три индикатора влево (причем Х5 — XV пропадают), а на месте ХО, XI, Х2 высвечивается код вновь нажатой кнопки (рис. 7.10,6, табл. 7.8).

Рис. 7.10. Состояния индикаторов порта вывода с адресом OOOQ:

а - до нажатия какой-либо из кнопок 0-7; б - после нажатия какой-либо из кнопок 0 — 7

Следовательно, нажав три необходимые кнопки из кнопок К1-К8, пользователь может набрать на восьми индикаторах порта OOOQ любое нужное ему двоичное число длиной 1 байт.

Рассмотрим теперь, какие специальные функции и как выполняются монитором.

Таблица 7.8

|

Кнопка |

|

Код в разрядах |

|

|

Y2 |

Y1 |

YO |

|

|

К1 |

0 |

0 |

0 |

|

К2 |

0 |

0 |

1 |

|

КЗ |

0 |

1 |

0 |

|

К4 |

0 |

1 |

1 |

|

К5 |

1 |

0 |

0 |

|

Кб |

1 |

0 |

1 |

|

К7 |

1 |

1 |

0 |

|

К8 |

1 |

1 |

1 |

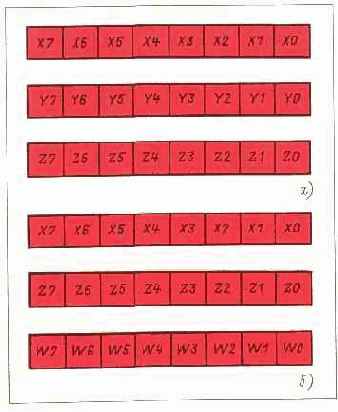

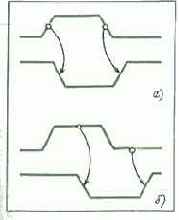

Смысл этих действий в том, что байт, хранящийся в регистре С, станет старшим байтом адреса той ячейки, с которой работает пользователь. Этот новый старший байт адреса высветится на индикаторах порта 002Q, а содержимое ячейки памяти с новым адресом, составленным из нового старшего байта и старого младшего байта адреса, высветится на индикаторах порта OOOQ. Таким образом, функция, выполняемая монитором при нажатии на кнопку К9 (СБ — старший байт), — это формирование старшего байта нового адреса. Его значение может быть предварительно введено с помощью кнопок К1 - К8 (цифры 0 — 7) в регистр С и высвечено на индикаторах порта OOOQ. На индикаторах пользователь видит следующее (рис. 7.11). Показания индикаторов порта OOOQ после нажатия СБ перемещаются на индикаторы порта 002Q (рис. 7.11,6), на индикаторах порта OOOQ после нажатия СБ высвечивается содержимое ячейки памяти с адресом, старший байт которого высвечен на индикаторах порта 002Q, а младший — порта 001Q.

Аналогичную функцию, только по формированию младшего байта адреса, выполняют кнопка К10 {МБ — младший байт) и связанный с ней фрагмент программы от команды М12: CPI 011Q до JMP M2. При нажатии на эту кнопку содержимое регистра С, высвеченное на индикаторах порта OOOQ, переписывается в регистр L, становясь младшим байтом адреса той ячейки, с которой работает пользователь, и высвечивается на индикаторах порта 001Q (рис. 7.12). На индикаторах порта OOOQ при этом высвечивается содержимое ячейки памяти с адресом, составленным из нового младшего байта и старого старшего байта.

Следующая кнопка К11 (И — индикация содержимого ячейки памяти и его изменение) выполняет две функции: просмотр содержимого ячеек памяти и изменение содержимого на новое в случае необходимости. При нажатии на эту кнопку подпрограмма SKL вырабатывает код 012Q, поэтому срабатывают команды условного перехода JNZ M12 и JNZ M13. После этого команда М13: CPI 012Q устанавливает флаг равенства нулю и команда JNZ M14 не осуществляет переход к М14.

Затем команда MOV M, С переписывает содержимое регистра С (это содер жимое пользователь видит на индикаторах порта OOOQ) в ячейку памяти, адрес которой содержится в паре регистров H-L (этот адрес пользователь видит на индикаторах портов 002Q и 001Q). Следующая команда INX Н увеличивает содержимое Н-Ьна единицу, а затем происходит безусловный переход (команда JMP М2) на фрагмент программы, который высвечивает на индикаторах адрес и содержимое следующей по порядку возрастания двоичных адресов ячейки памяти. Теперь ясно, что если нажимать только кнопку К11, то можно последовательно просматривать содержимое ячеек памяти в порядке возрастания их адресов (адрес высвечивается на индикаторах порта 002Q и 001Q, а содержимое — на OOOQ) ; но если между нажатием на кнопку К11 с помощью кнопок К1-К8 ввести в регистр С и на индикаторы порта OOOQ какое-либо двоичное число, то последующим нажатием на К11 можно переписать это число в текущую ячейку памяти и перейти к индикации адреса и содержимого следующей ячейки памяти.

Рис. 7.11. Состояния индикаторов портов вывода:

а - до нажатия кнопки СБ; б - после нажатия кнопки СБ

Кнопка К12 (П — пуск программы) выполняет функцию запуска программы, записанной пользователем в ОЗУ с адреса, который содержится в паре регистров H-L и высвечен на индикаторах портов 002Q и 001Q. При нажатии этой кнопки программа вырабатывает код 013Q и команды JNZ Ml2, JNZ M13, JNZ M14 осуществляют переход к М14: CPI 013Q. Эта команда устанавливает флаг равенства нулю, команда JNZ M4 не осуществляет переход к М4, и следующая команда PCHL загружает в счетчик команд содержимое пары регистров H-L, что вызывает переход к выполнению команды, расположенной по этому адресу.

Рис. 7.12. Состояния индикаторов портов вывода:

а - до нажатия кнопки МБ; б - после нажатия кнопки МБ

Кнопки К13-К16 не задействованы, и монитор не выполняет никаких функций при нажатии на них. Эти кнопки оставлены для дальнейшего расширения функций монитора.

Программа-монитор:

000000303 JMPM1

000 001 070

000 002 000

000070061 Ml: LXISP, 010 OOOQ

000071 000

000 072 020

000073041 LXIH.0060000

000 074 000

000 075 004

000076 116 М2: MOV С М

000077174 MOV A, M

000100323 OUT 0010

000 101 001

000102175 MOVA.L

000103323 OUT 0000

000 104 000

000105171 МЗ: MOV А, С

000106323 OUT 002Q

000 107 002

000110315 М4: CALL SKL

000 111 175

000112000

000113376 СР1 010Q

000 114 010

000115322 JNCM11

000 116 134

000117 000

000120107 MOVE, A

000121 171 MOV А, С

000122027 RAL

000 123 027 RAL

000124027 RAL

000125346 ANI 370Q

000 126 370

000127260 OR А В

000130117 MOV С, А

000 131 303 JMPM3

000 132 105

000 133 000

000134376 Mil: CPI 010Q

000 135010

000136302 JNZM12

000137 145

000 140 000

000 141 141 MOVH, С

000142303 JMPM2

000 143 076

000 144 000

000145376 M12: CPI011Q

000 146 Oil

000147302 JNZM13

000 150 156

000 151 000

000152151 MOVL, С

000153303 JMPM2

000 154 076

000 155 000

000156376 M13: CPI 012Q

000 157 012

000160302 JNZM14

000 161 170

000 162 000

000163161 MOVM, С

000 164 043 INX H

000 165 303 JMPM2

000 166 076

000 167 000

000170376 M14: CPI 013Q

000 171 013

000172302 JNZ M4

000 173 110

000 174 000

000175351 PCHL

000176000

000177076 SKL: MVI A, OOOQ

000 200 000

000201323 OUT003Q

000 202 003

000203333 M5: IN 003Q

000 204 003

000205346 ANI 017Q

000206 017

000207376 CPI017Q

000210 017

000 211 302 JNZM5

000 212 203

000 213 000

000214315 CALLDL

000 215 277

000 216 000

000217325 PUSH D

000 220 026 M8: MVI D, 003Q

000 221 003

000222036 MVIE, 376Q

000 223 376

000224173 M7: MOV A, E

000225323 OUT003Q

000 226 003

000 227 007 RLC

000230137 MOVE, A

000231333 IN003Q

000 232 003

000233346 ANI017Q

000 234 017

000235376 CPI017Q

000236 017

000 237 302 JNZ M6

000 240 254

000 241 000

000 242 025 DCR D

000 243 172 MOV A, D

000 244 376 CPI 377Q

000 245 377

000 246 302 JNZ M7

000 247 224

000 250 000

000251303 JMPM8

000 252 220

000 253 000

000254315 Мб: CALL DL

000 255 277

000 256 000

000257017 M10: RRC

000 260 322 JNC M9

000261 274

000 262 000

000 263 365 PUSH PSW

000264172 MOV A, D

000 265 306 ADI 004Q

000 266 004

000 267 127 MOV D, A

000270361 POP PSW

000271303 JMPM10

000 272 257 000 273 000

000274172 M9: MOV A, D

000275321 POP D

000276311 RET

000 277 365 DL: PUSH PSW

000 300 325 PUSH D

000301021 LXID, 0010160

000302016 000303 002

000 304 033 OCX D

000305 172 MOV A, D

000 306 263 ORA E

000 307 302 JNZ N

000310304 000311 000

000312321 POPD

000313361 POP PSW

000314311 RET

Теперь можно сформулировать инструкцию по работе на микро-ЭВМ.

ПРОГРАММИРОВАНИЕ ПМ-ЭВМ

Как уже отмечалось в гл. 3, ПМ-ЭВМ не имеет программного обеспечения, позволяющего пользоваться для решения задач языками высокого уровня. Поэтому запись программы для ПМ-ЭВМ осуществляется пользователем на машинном языке с применением команд описанных выше групп.

Полный перечень команд, приведенных в сжатой форме в табл. 4.1 — 4.3, должен быть хорошо известен пользователю, решающему свою задачу. Это даст ему возможность варьировать при составлении своих программ различными командами и способами их включения в программы с целью составления программ либо более коротких, либо экономящих используемую память, либо сокращающих время счета.

В ряде случаев способ решения той или иной задачи становится более понятным, если он представлен в виде специальной схемы, называемой схемой алгоритма решения и имеющей вид ориентированной сети с вершинами различных типов, соответствующими используемым операциям.

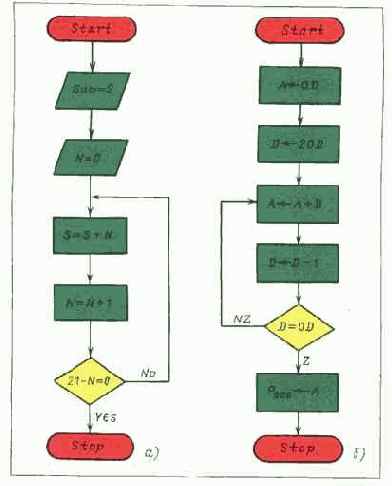

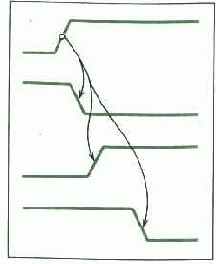

В качестве примера рассмотрим решение задачи суммирования первых 20 чисел натурального ряда, схема которой приведена на рис. 4.13,а.

Для реализации первых двух операторов (не считая Start) можно воспользоваться двухбайтовой командой MVI г, осуществляющей непосредственную загрузку в какой-либо регистр данных, содержащихся во втором байте команды (в данном случае - чисел OD). Для осуществления операции S = S + N можно воспользоваться командой ADD r, выполняющей суммирование содержимого какого-либо регистра с содержимым аккумулятора и запись результата в аккумулятор. Для выполнения операции N = N + 1 в машинном языке ПМ-ЭВМ предусмотрена специальная команда INR г, осуществляющая увеличение на единицу содержимого какого-либо регистра. Остается еще организовать в программе цикл с использованием условного оператора. Для этой цели подошла бы команда JNZ, осуществляющая переход в программе при отсутствии нуля в результате какой-либо предшествующей переходу операции (в нашем случае — операции вычитания: 21 — N).

Однако этого можно и не делать, построив несколько иначе схему решения задачи. Вместо того чтобы суммировать последовательно увеличивающиеся числа от О D до 20 D, можно суммировать последовательно уменьшающиеся числа от 20 D до OD. Тогда содержимое регистра, хранящего число N, на некотором шаге выполнения программы обратится в нуль и этот результат можно будет использовать при организации условного перехода.

Итак, новая схема алгоритма может быть построена следующим образом.

Шаг 1. Заносим число О D в аккумулятор (А).

Шаг 2. Заносим число 20 D в какой-нибудь регистр, например в регистр D.

Шаг 3. Суммируем содержимое регистров А и D.

Шаг 4. Уменьшаем содержимое регистра Она единицу.

Шаг 5. Если содержимое регистра Вне равно нулю, осуществляем переход к шагу 3; в противном случае переходим к следующему шагу.

Ш а г 6. Переписываем содержимое регистра А в какой-нибудь из портов вывода, например в порт Р0оо-

Ш а г 7. Конец работы программы.

Соответствующая схема представлена йа рис. 4.13,6.

Приступим к программированию этой схемы. Для этой цели нам понадобятся все указанные выше команды, за исключением команды INR г (увеличение содержимого регистра на единицу). Вместо нее следует взять команду DCR г (уменьшение содержимого регистра на единицу), которая будет использована применительно к регистру D. Кроме того, нам будут необходимы еще следующие две команды: OUT — двухбайтовая команда вывода данных из аккумулятора в порт вывода, определяемый адресом, содержащимся во втором байте команды, и однобайтовая команда HLT — останов программы. Коды всех используемых команд можно взять из таблицы, приведенной в приложении 1.

Для размещения всей программы нам понадобятся 12 ячеек памяти с номерами от 014QOOOQ до 014Q013Q. В первые две ячейки с номерами 014 000 и 014 001 поместим оба байта первой команды MVI A OOOQ загрузки аккумулятора (регистра А) числом OD. При этом в первую ячейку поместим восьмеричный код команды 076, а во вторую — содержимое второго байта этой команды — восьмеричный код числа OD (число 000).

В следующие две ячейки с номерами 014 002 и 014 003 поместим два байта следующей команды, загружающей регистр D десятичным числом 20. Восьмеричный код этой операции 026 будет находиться в первой ячейке, а восьмеричный код 024 десятичного числа 20 - во второй и т. д. В последнюю ячейку с номером 014 013 поместим восьмеричный код 166 команды HLT, осуществляющей останов программы. В табл. 4.5 приведен полный текст составленной программы вместе с комментарием. При организации цикла использована специальная метка Ml, указывающая на операцию, которую следует выполнить, если содержимое регистра D не равно нулю.

Рис. 4.13. Схемы алгоритмов для задачи сложения первых 20 чисел

Таблица 4.5

|

Адрес ячейки |

Код операции или содержимого второго или третьего байта |

Метка |

Мнемокод |

Комментарий |

|

014 000 |

076 |

|

MVI A OOOQ |

Загрузка регистра А числом OD |

|

014 001 |

000 |

|

|

Число OD |

|

014 002 |

026 |

|

MVI D 024Q |

Загрузка регистра D числом 20 D |

|

014003 |

024 |

|

|

Число 20 D |

|

014 004 |

202 |

Ml: |

ADDD |

Сложение содержимого регистров А и D |

|

014005 |

025 |

|

DCRD |

Уменьшение на единицу содержимого регистра D |

|

014 006 |

302 |

|

JNZM1 |

Переход к метке М 1 при отсутствии нуля |

|

014 007 |

004 |

|

|

Метка М 1 (адрес) |

|

014 010 |

014 |

|

|

Метка М 1 (адрес) |

|

014 011 |

323 |

|

OUT OOOQ |

Вывод данных из регистра А в порт рооо |

|

014 012 |

000 |

|

|

Номер порта |

|

014013 |

166 |

|

HLT |

Останов программы |

Перейдем теперь к рассмотрению работы конкретных схем отдельных функциональных блоков ПМ-ЭВМ, назначение которых было определено ранее.

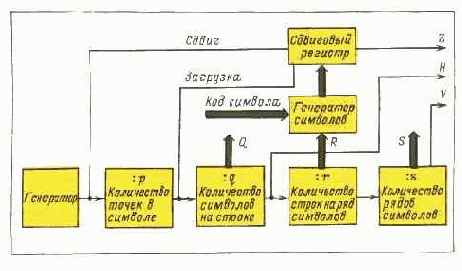

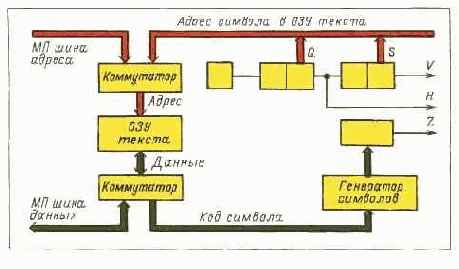

ПРОСТОЙ ГРАФИЧЕСКИЙ ДИСПЛЕЙ

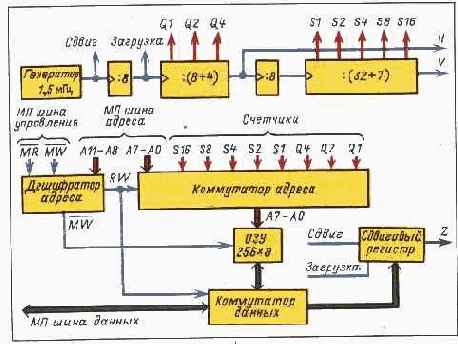

Запоминающее устройство на 256 слов по 8 бит позволяет отображать 2048 точек на экране в виде сетки 64x32 элемента. В этом случае знакогенератор не требуется, поскольку каждый бит из памяти прямо отображается без преобразования. Схема такого устройства индикации дана на рис. 10.9. Каждая точка формируется из восьми соседних горизонтальных строчек развертки.

Логика работы ТВ-дисплея довольно проста и может быть без труда реализована даже на такой простой вычислительной машине, как ПМ-ЭВМ. Вся сложность в том, что быстродействие ПМ-ЭВМ, да и многих других машин более высокого класса, недостаточно, чтобы уложиться в жесткие рамки телевизионного стандарта. Выход заключается либо в создании специализированного периферийного процессора — контроллера ЭЛТ, каковыми являются рассмотренные выше устройства (промышленностью выпускается специализированная микросхема КР580ВГ75 - программируемый контроллер ЭЛТ), либо в отступлении от стандарта, если требования к информационной емкости дисплея, как в нашем случае, не велики.

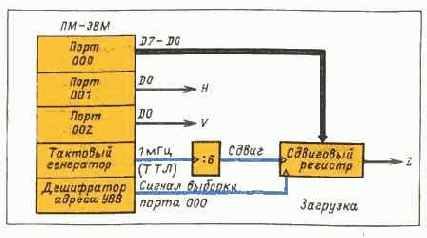

Покажем, что, не используя практически никакой дополнительной аппаратуры, можно реализовать вывод поля памяти объемом 256 байтов (сетка 64x32 элемента) на экран обычного осциллографа. Подключим к ПМ-ЭВМ схему, показанную на рис. 10.10. Здесь порт 000 служит для параллельной выдачи содержимого ячеек памяти. Сдвиговый регистр преобразует параллельный код в последовательный. Сигнал с выхода сдвигового регистра может быть подан непосредственно на вход Z модуляции яркости осциллографа. Порт 001 служит для вывода синхроимпульса строчной развертки Н, а порт 002 — для вывода синхроимпульса кадровой развертки V. Кадровая и строчная развертки могут быть сформированы с помощью простых пассивных цепей непосредственно из соответствующих синхроимпульсов. Выдаваемые портами 000, 001 и 002 сигналы формируются с помощью следующей программы:

014 000 176 Ml: MOV A, M 7 - количество тактов

014 001 323 OUT,OOOQ10 014 002 000

014 003 167 MOV M, А 7

014 004 000 NOP 4

014 005 054 INR L 5

014 006 035 DCRE 5

014 007 302 JNZ,M1 10

014 010 000

014 011 014

Итого: 48 тактов

Рис. 10.9. Схема приставки для формирования графической информации на экране ТВ

Эта часть программы выводит в порт 000 очередной байт из памяти. Команды MOV M, А и NOP вставлены, чтобы получить выраженную в тактах длительность этого фрагмента программы кратной восьми. В итоге получаем 48 тактов. Это значит, что стоящий на выходе сдвиговый регистр должен выдавать очередной разряд числа через каждые 6 тактов, чтобы завершить выдачу всех восьми разрядов за 48 тактов. После восьми циклов прохождения первого фрагмента программы содержимое регистра Е станет равным нулю и начнет исполняться следующий фрагмент программы, предназначенный для выдачи синхроимпульса строчной развертки, здесь же происходит и загрузка регистра Е:

Рис. 10.10. Схема приставки для формирования графической информации на экране осциллографа

014012257 XRAA 4

014013323 OUT.OOOQ 10

014 014 000

014015323 OUT,001Q 10

014016 001

014017036 MVIE, 010Q 7

014 020 010

014 021 000 NOP 4

014 022 000 NOP 4

014 023 000 NOP 4

014 024 000 NOP 4

014 025 000 NOP 4

014 026 000 NOP 4

014 027 000 NOP 4

014 030 000 NOP 4

014031000 NOP 4

014032057 СМА 4

014033323 OUT, 001Q Ю

014 034 001

014035025 DCRD 5

014036302 JNZ,M1 Ю

014037 000

014040014 ---------------

Итого: 56.тактов

Этот фрагмент программы имеет продолжительность 96 тактов, т. е. вдвое больше времени выдачи одного байта из памяти. Следовательно, общая продолжительность цикла строчной развертки составляет 48-8 + 96 = 480 тактов (т. е. 480 мкс). Количество строк определяется числом 32 (040Q), загружаемым в регистр D следующим фрагментом программы:

014041257 XRA, А 4

014042323 OUT, 002Q 10

014 043 002

014 044 026 MVI D, 040Q 7

014 045 040

014046041 LXIH, ADM 10

014 047 000

014050015

014051315 CALLINP 17

014 052 X

014053 Y

014 054 057 СМА 4

014055323 OUT, 002Q 10

014 056 002

014057303 JMP, Ml 10

014 060 000

014061 014

Итого: 72 + время исполнения ПП ввода IMP (3840 тактов)

В этом фрагменте происходит выдача синхроимпульса кадровой развертки и задается адрес начала массива информации, выводимой на дисплей. Отведя на обратный ход луча время, равное четверти длительности прямого хода луча для вертикальной развертки, получим период кадровой развертки, равный 480-32 + 480-8 = 19 200 мкс. Отсюда получаем частоту кадровой развертки, равную примерно 50 Гц, что нас вполне удовлетворяет. В последнем фрагменте программы, длящемся 3840 мкс, предусмотрен вызов ПП ввода информации в ОЗУ с клавиатуры или внешнего устройства для изменения картинки на экране дисплея. Эта ПП должна иметь строго определенную длительность, необходимую для стабильности параметров развертки. Если в этом промежутке времени исполняются другие программы неизвестной длительности, надо организовать систему с внешними прерываниями.

РЕАЛИЗАЦИЯ ДИАЛОГОВОГО РЕЖИМА

Диалоговый режим реализует

взаимодействие человека с вычислительной машиной. Наиболее употребительными техническими средствами, обеспечивающими обмен информацией между человеком и машиной в процессе диалога, являются клавишные устройства и устройства визуального отображения (дисплеи). Поскольку ПМ-ЭВМ имеет, хотя и ограниченные по своим возможностям, клавиатуру и светодиодную индикацию, можно попытаться организовать на ней диалоговый режим. Введем в ПМ-ЭВМ следующую программу, предназначенную для оценки реакции оператора в диалоговом режиме:

014000041 Ml: LXI H, TAB

014001 110

014002 014

014003257 М2: XRA А

014 004 323 OUT, OOOQ

014005 000

014006323 OUT.001Q

014007 001

014010323 OUT, 003Q

014011 003

014012107 MOV В, А

014 013 117 MOVC, A

014 014 057 CMA

014015323 OUT, 002Q

014 016 002

014017176 MOV A, M

014 020 267 ORA A

014021312 JZ,M1

014 022 000

014023014

0140243-15 M3: CALL DL

014025 277

014 026 000

014027075 DCRA

014030302 JNZ, M3

014031 024

014 032014

014033323 OUT, 002Q

014034 002

014035333 M4: IN, 003Q

014 036 003

014037057 CMA

014 040 267 ORA A

014041312 JZ.M6

014042061

014 043 014

014044171 MOV А, С

014045323 OUT, OOOQ

014 046 000

014047170 MOV А, В

014050323 OUT, 001Q

014051 001

014052333 M5: IN, 003Q

014 053 003

014 054 057 CMA

014055267 ORA A

014056302 JNZ,M5

014 057 052

014 060014

014061315 M6: CALLDL

014062277

014 063 000

014064171 MOV А, С

014 065 074 INR A

014 066 047 DAA

014067117 MOVC, A

014070170 MOV А, В

014071316 ACI, OOOQ

014 072 000

014073047 DAA

014074107 MOVB.A

014075376 CPI,005Q

014076005

014077332 JC, M4

014 100035

014 101 014

014102043 INXH

014 103 303 JMP, M2

014 104 003

014 105 014

014110377 TAB:

014 111 200

014 112300

014 113 330

014 114000

После ввода программы нажмем кнопки СБРОС и П. Порт 002 высветит число 377Q (все единицы), а индикаторы портов 001 и 000 погашены. Через неизвестный оператору интервал времени индикаторы порта 002 гаснут. В этот момент оператор должен нажать любую (кроме СБРОС) кнопку клавиатуры. В портах 001 и 000 высветится выраженное в двоично-десятичном коде время задержки между погасанием индикаторов порта 002 и нажатием кнопки.

Порт 001 индицирует десятки и единицы секунд (считая слева), а порт 000 — десятые и сотые доли секунды. После отпускания кнопки через заданный интервал времени индикаторы портов 001 и 000 гаснут, а индикаторы порта 002 снова загораются, чтобы погаснуть через неизвестный интервал времени. Если ни одна кнопка не нажата после погасания индикаторов порта 002, через заданный интервал времени они снова загорятся. Если кнопка нажата до погасания индикаторов, то портами 001 и 000 индицируется нулевая задержка, т. е. не загорается ни один индикатор.

Оценки времени реакции оператора (в секундах):

0,00 — 0,09 — ошибочное значение, Вы поторопились, попробуйте снова;

0,10 — 0,14 — исключительная, почти фантастическая реакция;

0,15 — 0,19 — очень хорошая;

0,20 — 0,24 -нормальная;

0,25 — 0,29 -посредственная;

0,30 — 0,34 — плохая;

0,35 — 5,00 - Вы, вероятно, уснули.

Программа может быть использована как для оценки, так и для тренировки реакции. Время задержки гашения индикаторов порта 002 задается количеством циклов задержки, начинающихся с метки МЗ. В аккумулятор при каждом замере заносятся последовательно числа из таблицы, хранящейся в ячейках памяти, начиная с адреса, задаваемого командой LXIH. Длина таблицы практически неограниченная. Если в таблице помещено число OOOQ, то при его занесении в аккумулятор на очередном шаге происходит возврат к началу программы и, следовательно, к началу таблицы. Цена младшего разряда, задающего задержку числа, равна задержке, вырабатываемой ПП DL, т. е. 10 мс. После того как индикаторы порта 002 погашены (команда по адресу 014Q 033Q) и до нажатия кнопки с помощью счетчика, организованного на регистровой паре В, подсчитывается количество циклов обращения к ПП DL (команды, начиная с метки Мб). В счетчиках используется команда DAA, поэтому результат получается в двоично-десятичном коде. При нажатии кнопки содержимое регистровой пары В выводится в порты 001 и 000. Счетчик циклов снова задействуется после отпускания кнопки, и после достижения заданного числа циклов происходит возврат к метке М2 программы, при этом регистровая пара Н инкрементируется, в результате чего при следующем замере в качестве параметра задержки извлекается следующее число из таблицы.Параметры, определяющие работу программы, помещаются по следующим адресам: 014Q 001Q, 014Q 002Q — адрес начала таблицы; 014Q 076Q — время, в течение которого индикаторы порта 002 погашены; цена младшего разряда — около 1 с.

Обратим внимание на то, что для ввода информации с клавиатуры не использована ПП SKL, так как при обращении к ней невозможно организовать счет времени (до нажатия кнопки процессор не выходит из ПП).

10

РЕКОМЕНДУЕМОЙ ЛИТЕРАТУРЫ

1. Нестеров П. В. Микропроцессоры 1. Архитектура и ее оценка. М.: Высшая школа, 1984.

2. Вайда Ф., Чакань А. Микро-ЭВМ: Пер. с венгер./ Под ред. В. В. Ста-шина. М.: Энергая, 1980.

3 Шаньгин В. Ф., Костин А. Е. Микропроцессоры 2. Организация вычислительных процессов на микро-ЭВМ. М.: Высшая школа, 1984.

4. Горячев А. В., Шишкевич А. А. Микропроцессоры 6. Информационно-управляющие вычислительные системы. М.: Высшая школа, 1984.

5. Клингман Э. Проектирование микропроцессорных систем. М.:

Мир, 1980.

6. Вуд А. Микропроцессоры в вопросах и ответах: Пер. с англ./ Под ред. Д. А. Поспелова. М.: Энергоатомиздат, 1985.

7. Поспелов Д. А. Логические методы анализа и синтеза схем. М.: Энергия, 1974.

8. Трачик В. Дискретные устройства автоматики: Пер. с польск./ Под ред. Д. А. Поспелова. М.: Энергия, 1978.

9. Коффрон Дж. Технические средства микропроцессорных систем: Практический курс: Пер. с англ. М.: Мир, 1983.

10. Интегральные микросхемы: Справочник/ Под ред. Б. В. Тараб-рина. М.: Радио и связь, 1983.

11. Григорьев В. Л Программное обеспечение микропроцессорных систем. М.: Энергоатомиздат, 1984.

12. Назаров Н. А. Программатор для микросхем К556РЕ4// В помощь радиолюбителю. 1983. Вып. 83. С. 26-31.

13. Хоровиц П., Хилл У. Искусство схемотехники: Пер. с англ./ Под ред. М. В. Гальперина. М.: Мир, 1983. Т. 1, Т 2.

14. Алексенко А. Г., Галицын А. А., Иванников А. Д. Премирование радиоэлектронной аппаратуры на микропроцессорах: Программирование, типовые решения, методы отладки. М.: Радио и связь, 1984.

15. Иванов Б. Н. Самодельный блок питания// В помощь радиолюбителю. 1983. Вып. 84. С. 62-73.

16. Васильев Н. П., Горовой В. Р. Микропроцессоры 5. Аппаратурно-программные средства отладки. М.: Высшая школа, 1984.

ОГЛАВЛЕНИЕ

Предисловие

Глава 1. ЧТО ТАКОЕ МИКРО-ЭВМ?

1.1. Типы микро-ЭВМ и области их применения

1.2. Можно ли самому построить ЭВМ?

Глава 2. КАКУЮ МИКРО-ЭВМ МЫ БУДЕМ СТРОИТЬ?

2.1. Основные блоки микро-ЭВМ

2.2. Содержимое центрального блока

2.3. Какую микро-ЭВМ мы будем называть "простейшей"?

Глава 3. НЕКОТОРЫЕ ОБЩИЕ СВЕДЕНИЯ О РАБОТЕ МИКРО-ЭВМ

3.1. Данные и программы

3.2. Основные логические операции

3.3. Основные арифметические операции

Глава 4. АРХИТЕКТУРА ПМ-ЭВМ И КОМПОНЕНТОВ

4.1. Конструктивное оформление ПМ-ЭВМ

4.2. Основные связи и структура шин

4.3. Общая функциональная схема ПМ-ЭВМ

4.4. Функциональная схема микропроцессора

4.5. Как микропроцессор выполняет команду?

4.6. Система команд и способы адресации

4.6.1. Группа команд пересылки данных

4.6.2. Группа арифметических команд

4.6.3. Группа логических команд

4.6.4. Группа команд переходов

4.6.5. Группа команд управления и работы со стеком

4.7. Программирование ПМ-ЭВМ

Глава 5. ИСПОЛЬЗУЕМЫЕ МИКРОСХЕМЫ

5.1. Общие вопросы

5.2. ТТЛ-входы и ТТЛ-выходы

5.3. Временные диаграммы

5.4. Микросхемы, реализующие логические функции

5.5. Микросхемы, содержащие элементы памяти

Глава 6. СТРУКТУРА И ФУНКЦИОНИРОВАНИЕ МИКРОПРОЦЕССОРНОГО БЛОКА

6.1. Микропроцессор КР580ИК80А

6.2. Синхронизация

6.3. Шины адреса, данных и управления

6.4. Тактовый генератор и схема пошагового исполнения программ

Глава 7. СХЕМЫ И ОСОБЕННОСТИ РАБОТЫ ОСНОВНЫХ БЛОКОВ ПМ-ЭВМ

7.1. Общие положения

7.2. Структура памяти

7.3. Клавиатура и индикация

7.4. Программа-монитор

7.5. Инструкция по работе на микро-ЭВМ

Глава 8. СБОРКА И ОТЛАДКА ПМ-ЭВМ

8.1. Этапы сборки и проверки узлов

8.2. Статический аппаратный эмулятор

8.3. Отладка в рабочем режиме

8.4. Подготовка ПМ-ЭВМ к работе

Глава 9. РАБОТА С ПМ-ЭВМ

9.1. Программируемый калькулятор

9.2. Программируемое управляющее устройство

9.3. Сбор и обработка данных

9.4. Реализация диалогового режима

Глава 10. РАСШИРЕНИЕ ВОЗМОЖНОСТЕЙ ПМ-ЭВМ

10.1. Клавиатура и индикация

10.2. Внешняя память

10.3. Накопитель на базе бытового магнитофона

10.4. Дисплей на базе бытового телевизора или осциллографа

10.5. Простой графический дисплей

10.6. Звуковая сигнализация

10.7. Другие возможности ПМ-ЭВМ

Приложение 1. Система команд микропроцессора КР580ИК80А

Приложение 2. Схема ПМ-ЭВМ

Приложение 3. Таблица элементов, используемых в схеме ПМ-ЭВМ

Список рекомендуемой литературы

Научно-популярное издание

БУРЕЕВ ЛЕВ НИКОЛАЕВИЧ

ДУДКО АЛЕКСЕЙ ЛЬВОВИЧ

ЗАХАРОВ ВАЛЕРИЙ НИКОЛАЕВИЧ

Простейшая микро-ЭВМ. Проектирование. Наладка. Использование

Редактор Д. А. Поспелов Редактор издательства 3. И. Михеева

Художественные редакторы Т. А. Дворецкова, Ю. В. Созанская

Технические редакторы Я. Н. Хотулева, О. Д. Кузнецова

Корректор Л. С. Тимохова

ББК 32.97 Б 91 УДК 681.31-181.48

Рецензент В. Ф. Корнюшко

Буреев Л. Н. и др.

В 91 Простейшая микро-ЭВМ: Проектирование. Наладка. Использование/ Л. Н. Буреев, А. Л. Дудко, В. Н. Захаров. — М.: Энергоатомиздат, 1989. — 216 с.: ил. — (Научно-попул. б-ка школьника).

ISBN 5-283-01482-7

На примере простейшей микро-ЭВМ рассматриваются возможности микропроцессорной техники. Построение описываемой в книге микро-ЭВМ доступно радиолюбителям - участникам школьного кружка. Составляющие микропроцессорной техники рассматриваются комплексно и иллюстрируются примерами.

Для широкого круга читателей, не обладающих специальной подготовкой в области электроники, вычислительной техники.

2405000000- 269

Б ---------------------- 2о4-оо

051 (01)-89

ISBN 5-283-01482-7

ББК 32.97

ИБ № 1723

Набор выполнен в издательстве. Подписано в печать с оригинала-макета 18.11.88. Т-20630. Формат 84 х 108 1/32. Бумага офсетная № 1. Гарнитура Пресс Роман. Печать офсетная. Усл. печ. л. 11,34. Усл. кр.-отт. 45,99. Уч.-изд. л. 12,95. Тираж 160 000 экз. Заказ 99, Цена 85 к.

Энергоатомиздат, ИЗ 114, Москва, М-114, Шлюзовая наб., 10.

Предприятие малообъемной книги дважды ордена Трудового Красного Знамени Ленинградского производственного объединения «Типография имени Ивана Федорова» Союзполиграфпрома при Государственном комитете СССР по делам издательств, полиграфии и книжной торговли. 192007, Ленинград, ул.Боровая, 51.

OCR Pirat

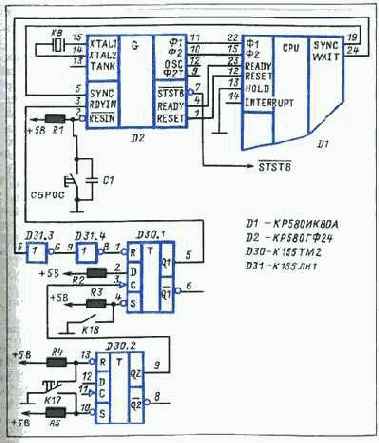

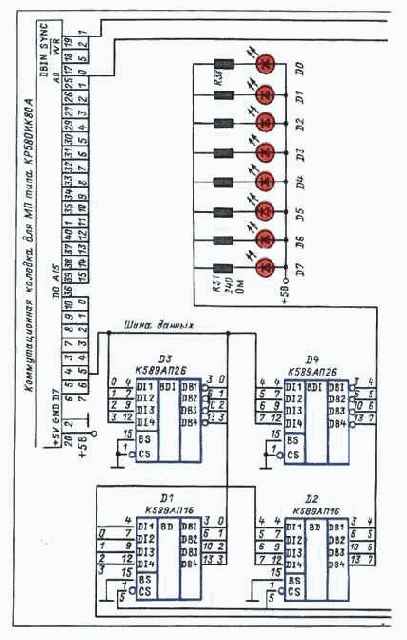

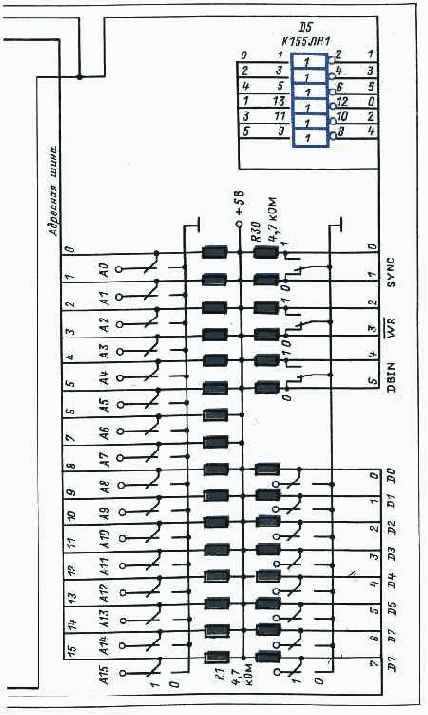

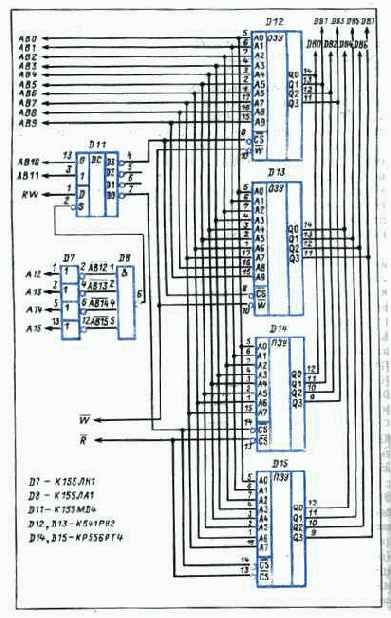

ШИНЫ АДРЕСА, ДАННЫХ И УПРАВЛЕНИЯ

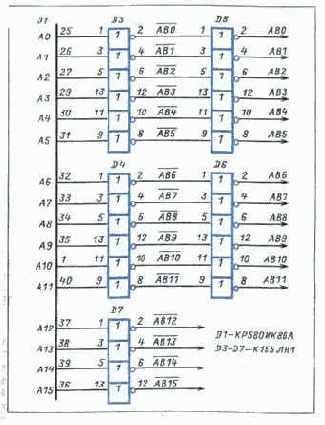

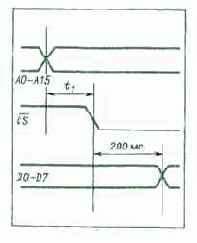

Шина адреса. Микропроцессор КР580ИК80А имеет 16-разрядную шину адреса А0-А15. Эта шина выполняет две функции. Первая функция состоит в передаче адреса ячейки памяти (стека) при обращении к памяти (стеку). С помощью 16 разрядов шины адреса можно адресовать 216 ячеек памяти (т. е. 64 Кбайта). Вторая функция шины адреса — это передача адреса внешнего устройства при выполнении команд IN и OUT. В этом случае адрес внешнего устройства появляется на линиях АО-А7 и дублируется на линиях А8-А15. Так как для передачи адреса внешнего устройства используется фактически только восемь разрядов, то можно адресовать 256 (2s) различных внешних устройств ввода/вывода.

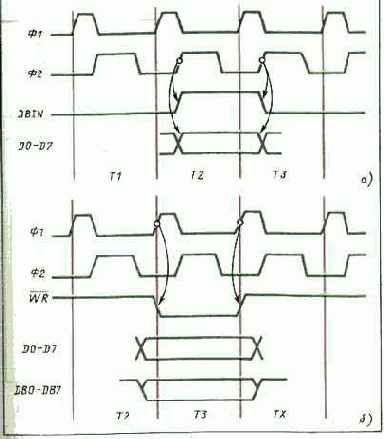

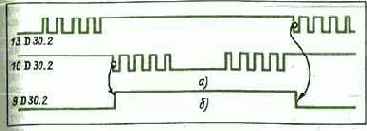

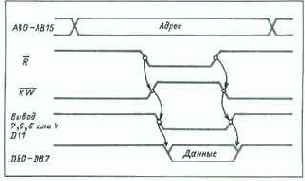

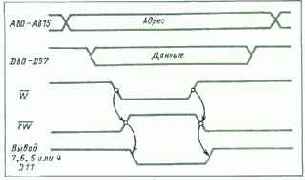

Временная диаграмма работы шины адреса приведена на рис. 6.3. Адрес появляется на шине по фронту сигнала Ф2 в такте Т1 и поддерживается три такта до фронта сигнала Ф2 в такте ТХ. Такт ТХ может быть четвертым тактом (Т4) машинного цикла, если цикл имеет более трех тактов, и может быть тактом Т1 следующего машинного цикла, если данный цикл имеет три такта.

Рис. 6.3. Временная анаграмма работы шины адреса

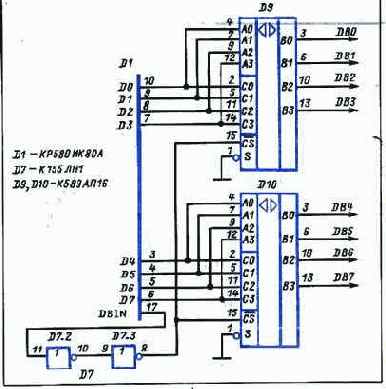

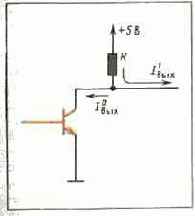

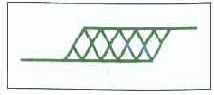

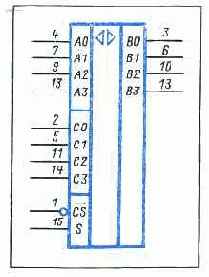

Каждая линия шины адреса является ТТЛ-выходом с тремя состояниями и нагрузочной способностью, равной единице. Так как шину адреса необходимо подавать на многие блоки ПМ-ЭВМ, то необходимо буферизовать ее линии, т. е. увеличить их нагрузочную способность. Для этого каждая линия подключается к входу схемы, состоящей из двух последовательно включенных инверторов (рис. 6.4). В результате на выходе второго инвертора имеется сигнал такого же уровня, как и на входе первого, но выход инвертора микросхемы К155ЛН1 имеет нагрузочную способность, равную 10.

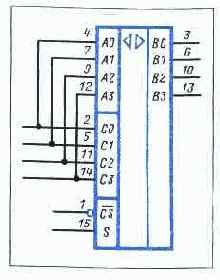

Шина данных. Микропроцессор КР580ИК80А имеет 8-разрядную двунаправленную шину данных DO — D7. Шина данных выполняет две функции. Первая функция — передача управляющего слова, вторая — обмен информацией между регистрами микропроцессора и блоками микро-ЭВМ. Шина данных — единственная двунаправленная шина микропроцессора. Ее выходы также являются выходами с тремя состояниями.

Рассмотрим функцию передачи управляющего слова. Известно (см. § 6.2), что микропроцессор КР580ИК80А имеет 10 типов машинных циклов. Информация о том, какого типа цикл будет выполняться, передается в начале каждого цикла по линиям шины данных и называется управляющим словом. Все управляющие слова перечислены в табл. 6.2. Управляющее слово или только его часть можно запомнить с помощью дополнительных триггеров и использовать затем для формирования сигналов шины управления. Как это делается, будет описано ниже.

Рис. 6.4. Шина адреса

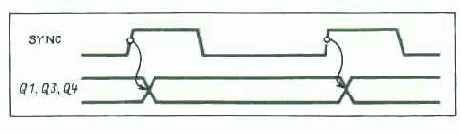

Для того чтобы показать, что идет процесс передачи управляющего слова, используется выход микропроцессора SYNC. Временная диаграмма приводится на рис. 6.5. Из нее видно, что передача управляющего слова по шине данных начинается по фронту сигнала Ф2 в такте Т1 и заканчивается по тому же фронту сигнала Ф2 в такте Т2.

Рис. 6.5. Временная диаграмма процесса передачи управляющего слова

Рассмотрим вторую функцию шины данных — обмен информацией между регистрами микропроцессора и блоками микро-ЭВМ. Во время циклов ВЫБОРКА КОМАНДЫ, ЧТЕНИЕ ИЗ ПАМЯТИ, ЧТЕНИЕ ИЗ СТЕКА, ВВОД С ВНЕШНЕГО УСТРОЙСТВА, ПРЕРЫВАНИЕ информация передается по шине данных в один из внутренних регистров микропроцессора из какого-либо блока микро-ЭВМ, а во время циклов ЗАПИСЬ В ПАМЯТЬ, ЗАПИСЬ В СТЕК, ВЫВОД НА ВНЕШНЕЕ УСТРОЙСТВО - из внутреннего регистра в какой-либо блок.

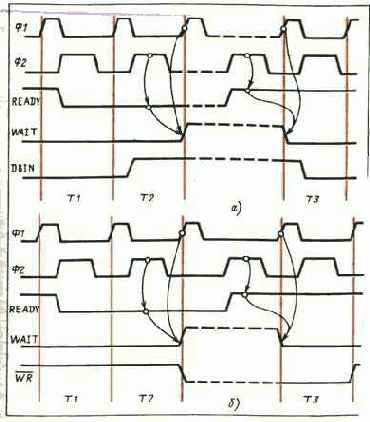

Для указания направления передачи информации по шине данных микропроцессор имеет два выхода: DBIN и WR. Когда информация передается в микропроцессор, то в этом машинном цикле на выходе DBIN появляется высокий уровень (рис. 6.6,а). Сигнал DBIN появляется по фронту сигнала Ф2 в такте Т2 и снимается по фронту Ф2 в такте ТЗ. Именно в это время внешние схемы должны поместить на шину данных код, который должен быть записан в один из внутренних регистров. Когда информация передается из микропроцессора, то в этом машинном цикле вырабатывается сигнал WR низкого уровня (рис. 6.6,6). Этот сигнал вырабатывается по фронту сигнала Ф1 в такте Т2 и снимается по фронту Ф1 в такте Т4 этого же машинного цикла (если цикл состоит более чем из трех тактов) или в такте Т1 следующего машинного цикла (если данный цикл состоит из трех тактов).

На шине данных ЕЮ — D7 немного ранее появления сигнала WR микропроцессор помещает данные и снимает их позднее снятия сигнала WR, поэтому внешние схемы могут использовать этот сигнал для управления записью информации.

Рис. 6.6. Временная диаграмма работы шины данных

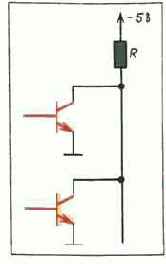

Каждая линия шины данных имеет единичную нагрузочную способность и поэтому нуждается в буферизации. Поскольку линии шины данных двунаправленны, необходим и двунаправленный буфер. Схема такого буфера, состоящая из двух микросхем К589АП16 (D9, D10), приводится на рис. 6.7. На входы 1 микросхем D9, D10 подан низкий уровень, и поэтому они работают все время в режиме передачи информации. Направление передачи определяется уровнем буферизованного сигнала DBIN, который подключен к входам 15 микросхем D9, D10. 3аметим, что направление передачи не управляется сигналами WR и SYNC .

Если уровень сигнала DBIN высокий, то шинные формирователи передают информацию в направлении к микропроцессору (от DBO — DB7 к DO — D7), если нет — то в обратном направлении (от ЕЮ — D7 к DBO — DB7), т. е. направление передачи шинных формирователей при низком уровне сигнала DBIN соответствует тому, которое должно быть при выработке сигналов WR и SYNC.

Рис. 6.7. Шина данных

Рис. 6.8. Шина управления

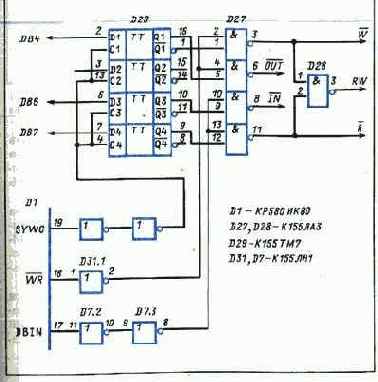

Шина управления. Микропроцессор КР580ИК80А не обладает готовой шиной управления, как шиной адреса и шиной данных. Поэтому эта шина организуется с помощью дополнительной внешней схемы (микросхемы D27, D29), называемой иногда системным контроллером (СК), которая использует управляющее слово и управляющие сигналы микропроцессора (рис. 6.8). Часть разрядов управляющего слова (D4, D6, D7) фиксируется в триггерах микросхемы К155ТМ7 (D29) по срезу сигнала SYNC (рис. 6.9). Сигнал SYNC пропущен через два инвертора для увеличения нагрузочной способности (эта схема, хотя и работоспособна, не будет применяться в ПМ-ЭВМ). Позднее будет приведена схема для фиксации управляющего слова, где сигнал на управляющие входы триггеров будет вырабатываться с помощью микросхемы КР580ГФ24.

Сигналы шины управления вырабатываются с помощью сигналов с выходов триггеров микросхем D29 и сигналов DBIN и WR.

Рис. 6.9. Временная диаграмма работы фиксаторов управляющего слова

В ПМ-ЭВМ команды, данные и содержимое стека хранятся в едином блоке памяти, состоящем из ОЗУ и ПЗУ. Поэтому Для управления чтением из блока достаточно иметь один сигнал R, который будет вырабатываться при выполнении машинных циклов ВЫБОРКА КОМАНДЫ, ЧТЕНИЕ ИЗ ПАМЯТИ, ЧТЕНИЕ ИЗ СТЕКА. Назовем условно эту группу циклов ЧТЕНИЕ. Для управления записью в блок также достаточно иметь один сигнал W, который будет вырабатываться при выполнении машинных циклов ЗАПИСЬ В ПАМЯТЬ, ЗАПИСЬ В СТЕК. Эту группу назовем ЗАПИСЬ.

Для управления вводом и выводом на внешние устройства необходимы два сигнала OUT и IN, которые будут вырабатываться при выполнении циклов ВЫВОД НА ВНЕШНЕЕ УСТРОЙСТВО и ВВОД С ВНЕШНЕГО УСТРОЙСТВА соответственно.

Формирование сигналов шины управления поясним, пользуясь табл. 6.3.

Таблица 6.3

|

Тип цикла или группы циклов |

Вырабатываемый сигнал DBIN или WR |

Используемый разряд |

Уровень напряжения на выхо дах триггеров D29 микросхемы |

Вырабаты- ваемый сигнал шины управ- ления |

|||

|

9 |

1 |

16 |

10 |

||||

|

ЧТЕНИЕ |

DBIN |

D7 |

Н |

Н |

L |

L |

R, RW |

|

ЗАПИСЬ |

WR |

D4 |

L |

Н |

L |

L |

W, RW |

|

ВЫВОД НА ВНЕШНЕЕ УСТРОЙСТВО |

WR |

D4 |

L |

L |

Н |

L |

OUT |

|

вводе ВНЕШНЕГО УСТРОЙ- СТВА |

DBIN |

D6 |

L H |

|

L |

H |

IN |

Рис. 6.10. Временная диаграмма циклов чтения и записи с переходом в режим ожидания:

а - цикл чтения; б - цикл записи

Для формирования сигнала R естественно воспользоваться разрядом D7 управляющего слова, так как именно в этом разряде имеется сигнал высокого уровня в циклах группы ЧТЕНИЕ (см. табл. 6.2), а для формирования сигналов OUT и IN — разрядами D4 и D6, потому что именно в этих разрядах сигнал имеет высокий уровень при выполнении соответствующих циклов и низкий уровень во всех остальных циклах.

Сложнее дело обстоит с формированием сигнала W для циклов группы

ЗАПИСЬ. Казалось, было бы естественно воспользоваться разрядом D1 управляющего слова, в котором передается сигнал низкого уровня для циклов группы ЗАПИСЬ. Но в этом разряде сигнал низкого уровня бывает также и в цикле ВЫВОД НА ВНЕШНЕЕ УСТРОЙСТВО, и так как в этом цикле также вырабатывается сигнал WR, то пришлось бы усложнять схему, чтобы сформировать два разных сигнала W и OUT. Поэтому для формирования сигнала W используется инвертированный разряд D4. Соответствующий ему сигнал снимается с инверсного выхода триггера (вывод 7). Этот сигнал имеет высокий уровень и для циклов группы ЧТЕНИЕ и ВВОД С ВНЕШНЕГО УСТРОЙСТВА (см. табл. 6.2), но при этом не формируются сигналы W и OUT (так как не в ырабатывается сигнал WR), а формируются лишь сигналы R и IN (так как вырабатывается сигнал DBIN).

Сигнал высокого уровня RW формируется из сигнала R или W и управляет работой дешифратора адреса (см. § 7.2). В заключение опишем еще некоторые управляющие сигналы микропроцессора КР580ИК80А и их функции.

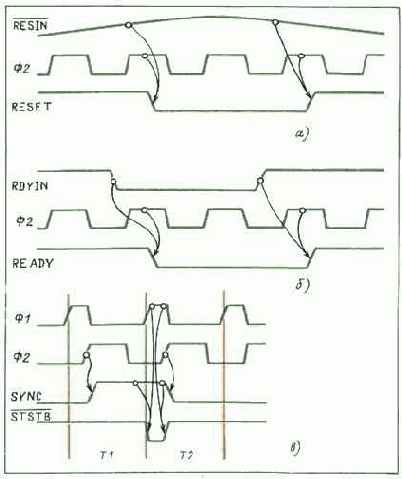

Вход READY используется для того, чтобы удлинить циклы ввода и вывода информации в микропроцессор и обеспечить таким образом возможность его работы с менее быстродействующими устройствами. Если во время высокого уровня сигнала Ф2 в такте Т2 какого-либо цикла на вход READY подается высокий уровень, то происходит нормальный цикл ввода или вывода информации. Если же подается низкий уровень, то микропроцессор с этого момента прекращает свою работу, сохраняя на всех выходах имеющиеся уровни сигналов (рис. 6.10). Такой режим называется режимом ожидания. Микропроцессор сигнализирует о том, что он находится в режиме ожидания, выработкой сигнала WAIT высокого уровня. В режиме ожидания микропроцессор не выполняет никаких операций и может находиться как угодно долго — до тех пор, пока не будет подан сигнал READY высокого уровня. После этого он завершает начатую операцию и продолжает далее свою работу.

Вход RESET используется для начального запуска микропроцессора и для повторных перезапусков. При подаче высокого уровня на этот вход микропроцессор прекращает свою работу, помещает во все разряды счетчика команд нули и бездействует до тех пор, пока на входе RESET остается высокий уровень. Как только высокий уровень снимается, он начинает выполнять команду, расположенную в ячейке памяти с нулевым адресом.

6.4. ТАКТОВЫЙ ГЕНЕРАТОР

И СХЕМА ПОШАГОВОГО ИСПОЛНЕНИЯ ПРОГРАММ

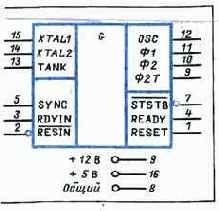

Для того чтобы получить тактовые импульсы с необходимыми для микропроцессора КР580ИК80А параметрами (см. § 6.2, рис. 6.2), можно использовать микросхему КР580ГФ24 (рис. 6.11, табл. 6.4). Эта микросхема является тактовым генератором, специально сконструированным для данного микропроцессора, и выполняет еще ряд дополнительных функций.

Т а б л и ц а 6.4

|

Название |

Назначение вывода |

|

XTAL1 XTAL2 |

Выводы для подключения кварцевого резонатора |

|

TANK |

Вывод, используемый при применении кварцевого резонатора с обертоном |

|

OSC |

Выход для синусоидального сигнала с частотой кварцевого резонатора |

|

Ф1.Ф2 |

Выходы для тактовых импульсов |

|

Ф2Т |

Выход для тактовых импульсов Ф2, но ТТЛ-уровня |

|

SYNC |

Вход для сигнала SYNC микропроцессора |

|

STSTB |

Выход для синхронизированного сигнала SYNC |

|

- |

Вход для асинхронного сигнала сброса |

|

RESIN |

|

|

RESET |

Выход для синхронизированного сигнала RESET микропроцессора |

|

RDYIN |

Вход для асинхронного сигнала готовности |

|

READY |

Выход для синхронизированного сигнала READY микропроцессора |

Рис. 6.12. Временные диаграммы синхронизации сигналов при помощи КР580ГФ24:

а - сигнал RESET; б - сигнал READY; в - сигнал SYNC